Altera Triple Speed Ethernet MegaCore Function User Manual

Page 102

• For PCS registers, map the registers to the dword offsets in the MAC register space before you convert

the dword offsets to byte offsets:

•

if_mode

word offset = 0x14

•

if_mode

dword offset = 0x80 + 0x14 = 0x94

•

if_mode

byte offset = 0x94 × 4 = 0x250

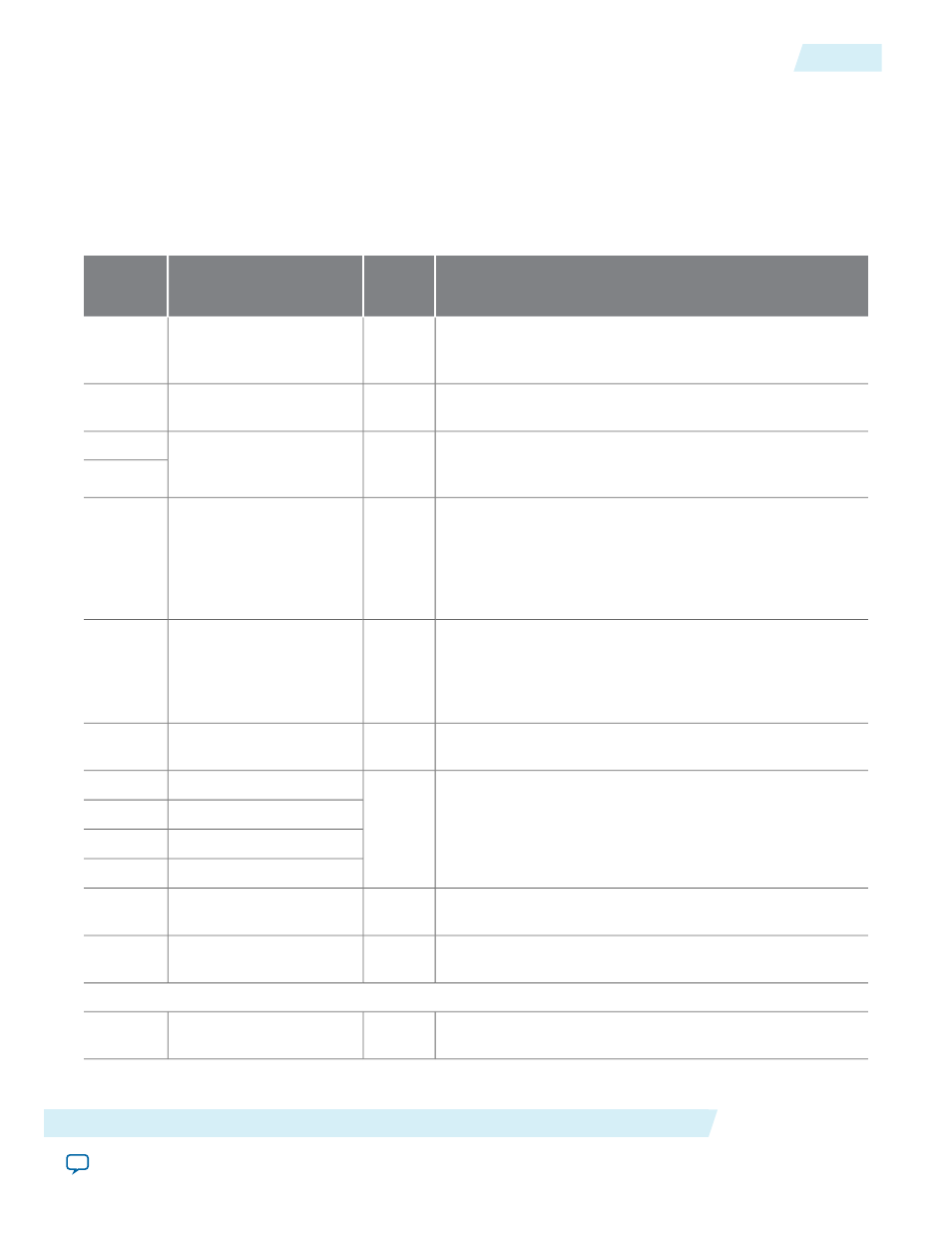

Table 6-12: PCS Configuration Registers

Description

R/W

Register Name

Word

Offset

PCS control register. Use this register to control and

configure the PCS function. For the bit description, see

Control Register (Word Offset 0x00)

on page 6-20.

RW

control

0x00

Status register. Provides information on the operation of

the PCS function.

RO

status

0x01

32-bit PHY identification register. This register is set to the

value of the PHY ID parameter. Bits 31:16 are written to

word offset 0x02. Bits 15:0 are written to word offset 0x03.

RO

phy_identifier

0x02

0x03

Use this register to advertise the device abilities to a link

partner during auto-negotiation. In SGMII MAC mode, the

PHY does not use this register during auto-negotiation. For

the register bits description in 1000BASE-X and SGMII

mode, see

on page 6-23 and

on page 6-25.

RW

dev_ability

0x04

Contains the device abilities advertised by the link partner

during auto-negotiation. For the register bits description in

1000BASE-X and SGMII mode, refer to

on

page 6-23 and

SGMII PHY Mode Auto Negotiation

on

page 6-25, respectively.

RO

partner_ability

0x05

Auto-negotiation expansion register. Contains the PCS

function capability and auto-negotiation status.

RO

an_expansion

0x06

The PCS function does not support these features. These

registers are always set to 0x0000 and any write access to

the registers is ignored.

RO

device_next_page

0x07

partner_next_page

0x08

master_slave_cntl

0x09

master_slave_stat

0x0A

—

—

Reserved

0x0B –

0x0E

The PCS function does not implement extended status

registers.

RO

extended_status

0x0F

Specific Extended Registers

Scratch register. Provides a memory location to test register

read and write operations.

RW

scratch

0x10

Altera Corporation

Configuration Register Space

6-19

PCS Configuration Register Space

UG-01008

2014.06.30