Packet classifier ingress control signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 214

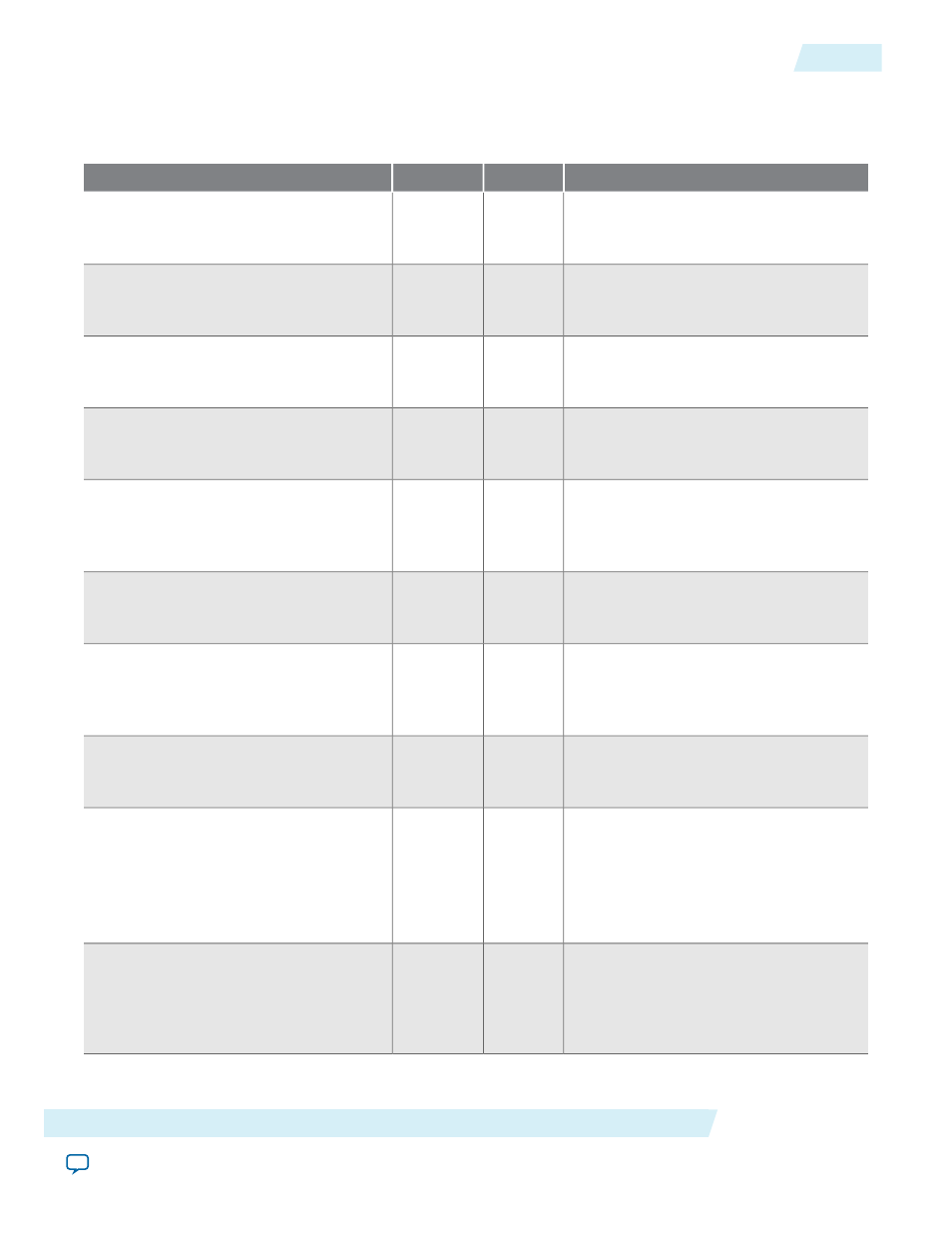

Packet Classifier Ingress Control Signals

Table E-4: Ingress Control Signals for the Packet Classifier

Description

Width

Direction

Signal

96-bit format of ingress timestamp that

holds data so that the output can align

with the start of an incoming packet.

96

Input

tx_etstamp_ins_ctrl_in_ingress_

timestamp_96b

64-bit format of ingress timestamp that

holds data so that the output can align

with the start of an incoming packet.

64

Input

tx_etstamp_ins_ctrl_in_ingress_

timestamp_64b

96-bit format of ingress timestamp that

holds data so that the output can align

with the start of an outgoing packet.

96

Output

tx_etstamp_ins_ctrl_out_ingress_

timestamp_96b

64-bit format of ingress timestamp that

holds data so that the output can align

with the start of an outgoing packet.

64

Output

tx_etstamp_ins_ctrl_out_ingress_

timestamp_64b

Assert this signal when timestamp is

required for the particular frame. This

signal must be aligned to the start of an

incoming packet.

1

Input

tx_egress_timestamp_request_in_

valid

A width-configurable fingerprint that

correlates timestamps for incoming

packets.

4

Input

tx_egress_timestamp_request_in_

fingerprint

Assert this signal when timestamp is

required for the particular frame. This

signal must be aligned to the start of an

outgoing packet.

1

Output

tx_egress_timestamp_request_out_

valid

A width-configurable fingerprint that

correlates timestamps for outgoing

packets.

4

Output

tx_egress_timestamp_request_out_

fingerprint

Determines the clock mode.

• 00: Ordinary clock

• 01: Boundary clock

• 10: End-to-end transparent clock

• 11: Peer-to-peer transparent clock

2

Input

clock mode

Indicates whether or not a packet

contains CRC.

• 1: Packet contains CRC

• 0: Packet does not contain CRC

1

Input

pkt_with_crc

Altera Corporation

Packet Classifier

E-3

Packet Classifier Ingress Control Signals

UG-01008

2014.06.30