Supplementary address (dword offset 0xc0 – 0xc7), Supplementary address (dword offset, 0xc0 – 0xc7) – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 98

Supplementary Address (Dword Offset 0xC0 – 0xC7)

A software reset has no impact on these registers. MAC supplementary addresses are not available in 10/100

and 1000 Small MAC variations.

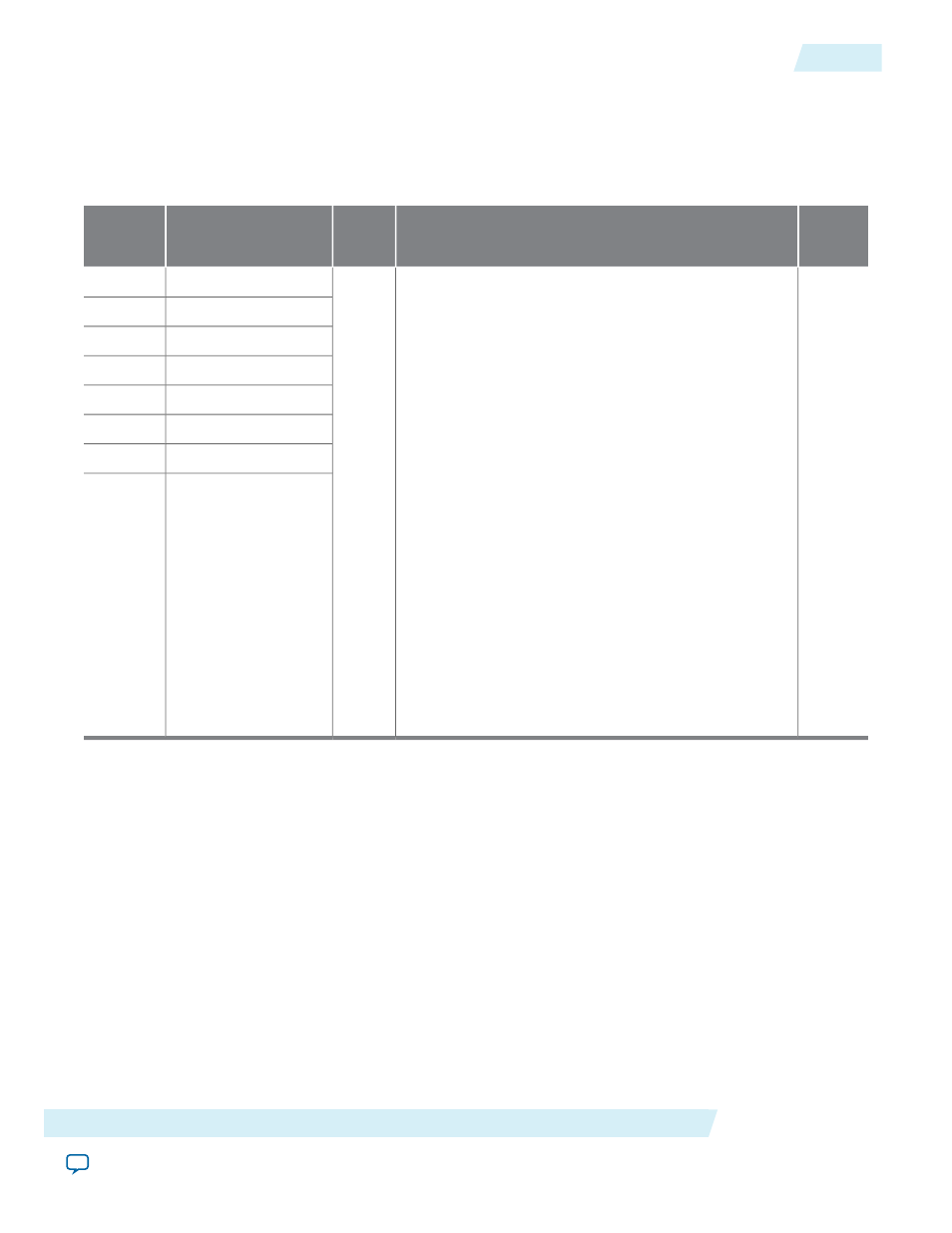

Table 6-6: Supplementary Address Registers

HW Reset

Description

R/W

Name

Dword

Offset

0

You can specify up to four 6-byte supplementary addresses:

• smac_0_0/1

• smac_1_0/1

• smac_2_0/1

• smac_3_0/1

Map the supplementary addresses to the respective registers

in the same manner as the primary MAC address. Refer to

the description of mac_0 and ma

c_1

.

The MAC function uses the supplementary addresses for

the following operations:

• to filter unicast frames when the promiscuous mode is

disabled (refer to

Command_Config Register (Dword

on page 6-7 for the description of the

PROMIS_EN

bit).

• to replace the source address in transmit frames received

from the user application when address insertion is

enabled (refer to

Command_Config Register (Dword

on page 6-7 for the description of the

TX_ADDR_INS

and

TX_ADDR_SEL

bits).

If you do not require the use of supplementary addresses,

configure them to the primary address.

RW

smac_0_0

0xC0

smac_0_1

0xC1

smac_1_0

0xC2

smac_1_1

0xC3

smac_2_0

0xC4

smac_2_1

0xC5

smac_3_0

0xC6

smac_3_1

0xC7

Altera Corporation

Configuration Register Space

6-15

Supplementary Address (Dword Offset 0xC0 – 0xC7)

UG-01008

2014.06.30