Altera Triple Speed Ethernet MegaCore Function User Manual

Page 211

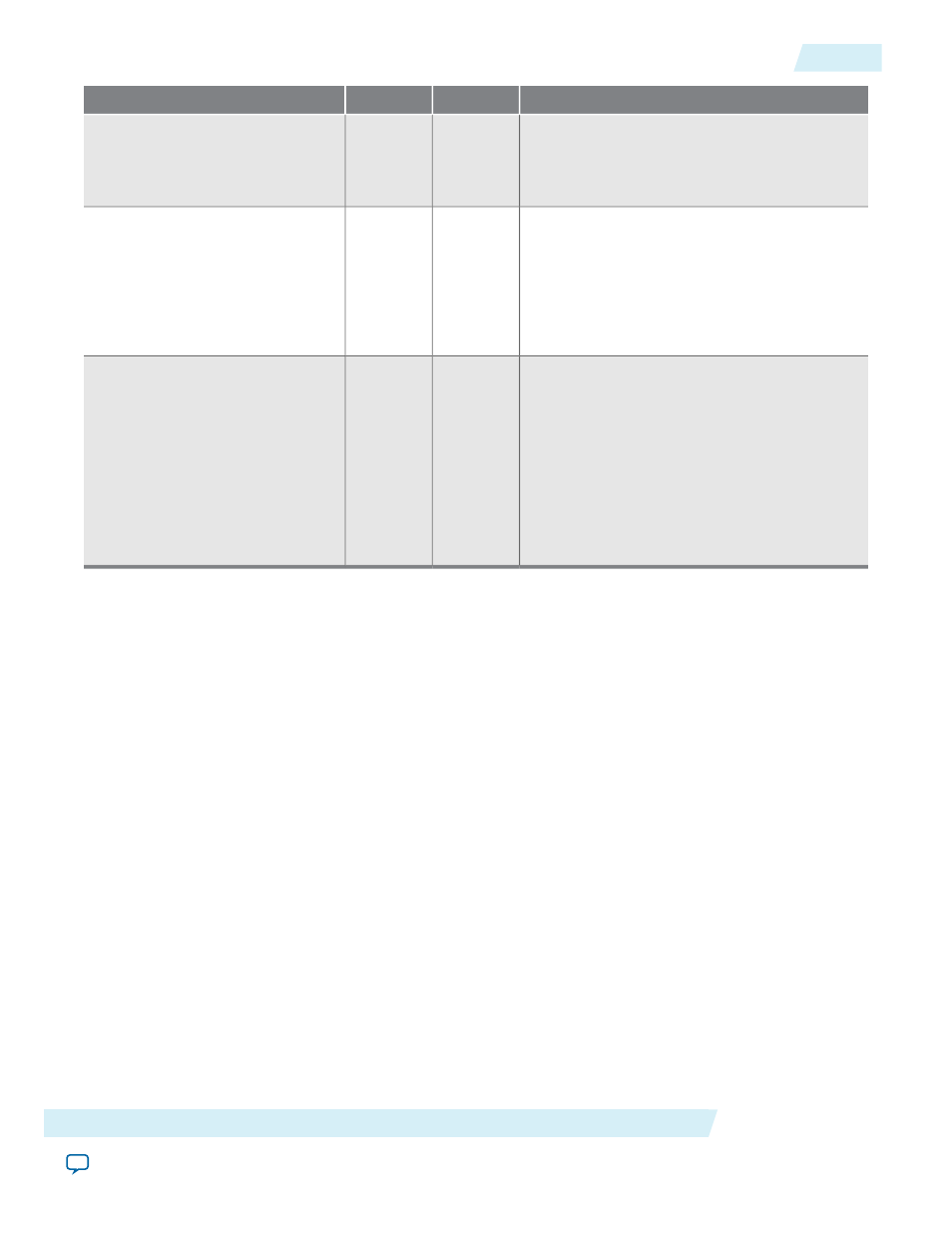

Description

Width

Direction

Signal

This signal carries the 64-bit or 96-bit format

data for the time of day from the master ToD.

The width of this signal is determined by the

TOD_MODE

parameter.

1

Input

tod_master_data

This signal indicates that the

tod_data_slave

signal is valid and ready to be loaded into the

slave ToD clock in the following cycle.

This signal will only be high for 1 cycle every

time a new time of day is successfully synchro-

nized to the slave clock domain.

tod_slave_valid

This signal carries the 64-bit or 96-bit format

synchronized time of day that is ready to be

loaded into the slave clock domain. The width

of this signal is determined by the

TOD_MODE

parameter.

The synchronized time of day will be 1 slave

clock period bigger than the master ToD

because it takes 1 slave clock cycle to load this

data into the slave ToD.

1

Input

tod_slave_data[n-1:0]

Altera Corporation

ToD Synchronizer

D-5

ToD Synchronizer Interface Signals

UG-01008

2014.06.30