Mii/gmii/rgmii signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 124

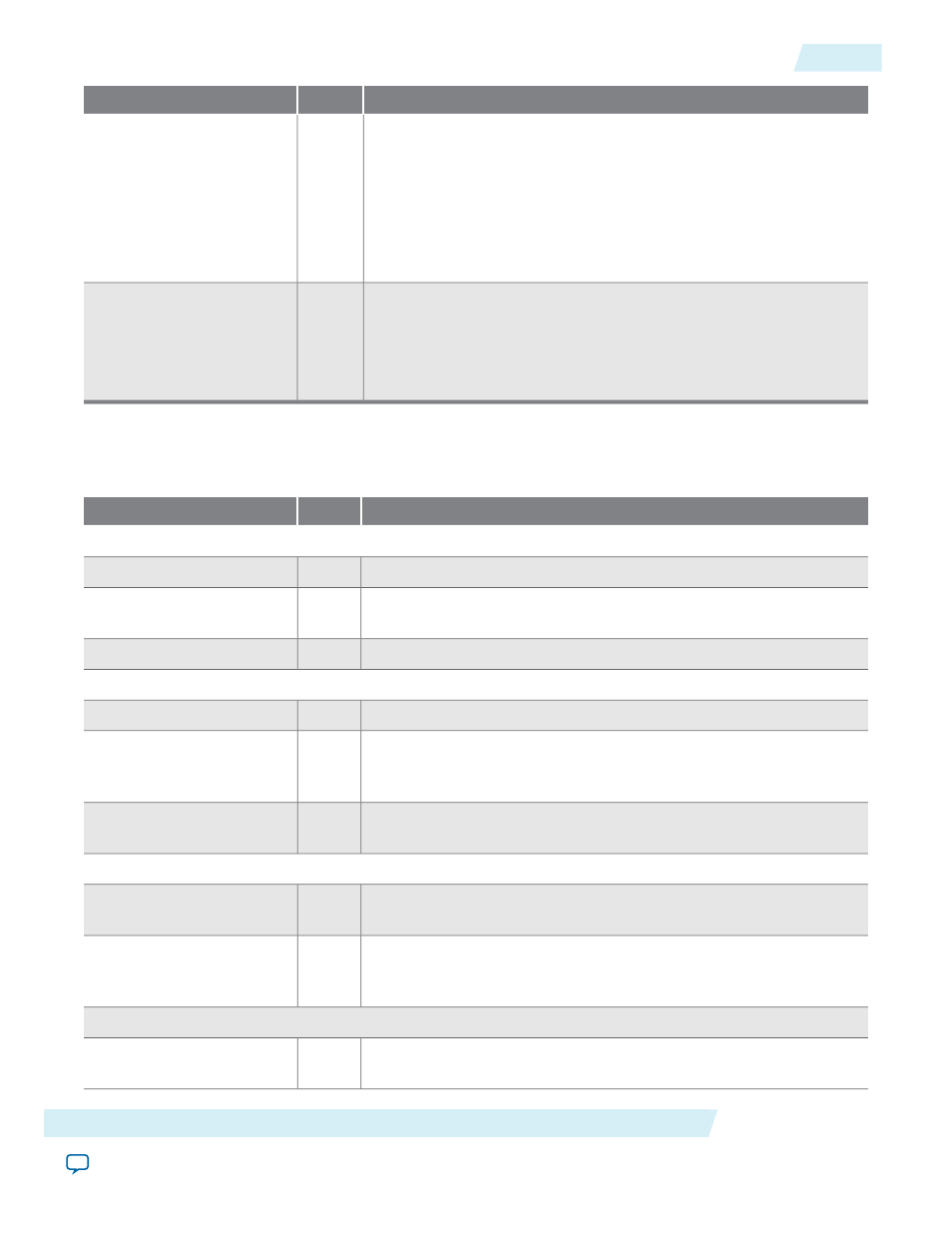

Description

I/O

Name

Assert this active-low signal to put the node into a power-down state.

If magic packets are supported (the

MAGIC_ENA

bit in the

command_

config

register is set to 1), the receiver logic stops writing data to the

receive FIFO buffer and the magic packet detection logic is enabled.

Setting this signal to 1 restores the normal frame reception mode.

This signal is present only if the Enable magic packet detection option

is turned on.

I

magic_slee

p_n

If the MAC function is in the power-down state, the MAC function

asserts this signal to indicate that a magic packet has been detected

and the node is requested to restore its normal frame reception mode.

This signal is present only if the Enable magic packet detection option

is turned on.

0

magic_wakeup

MII/GMII/RGMII Signals

Table 7-10: GMII/RGMII/MII Signals

Description

I/O

Name

GMII Transmit

GMII transmit data bus.

I

gm_tx_d[7:0]

Asserted to indicate that the data on the GMII transmit data bus is

valid.

O

gm_tx_en

Asserted to indicate to the PHY that the frame sent is invalid.

O

gm_tx_err

GMII Receive

GMII receive data bus.

I

gm_rx_d[7:0]

Assert this signal to indicate that the data on the GMII receive data bus

is valid. Keep this signal asserted during frame reception, from the first

preamble byte until the last byte of the CRC field is received.

I

gm_rx_dv

The PHY asserts this signal to indicate that the receive frame contains

errors.

I

gm_rx_err

RGMII Transmit

RGMII transmit data bus. Drives

gm_tx_d[3:0]

on the positive edge

of

tx_clk

and

gm_tx_d[7:4]

on the negative edge of

tx_clk

.

O

rgmii_out[3:0]

Control output signal. Drives

gm_tx_en

on the positive edge of

tx_clk

and a logical derivative of (

gm_tx_en XOR gm_tx_err)

on the negative

edge of

tx_clk

.

O

tx_control

RGMII Receive

RGMII receive data bus. Expects

gm_rx_d[3:0]

on the positive edge

of

rx_clk

and

gm_rx_d[7:4]

on the negative edge of

rx_clk

.

I

rgmii_in[3:0]

Altera Corporation

Interface Signals

7-9

MII/GMII/RGMII Signals

UG-01008

2014.06.30