Tod clock configuration register space – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 205

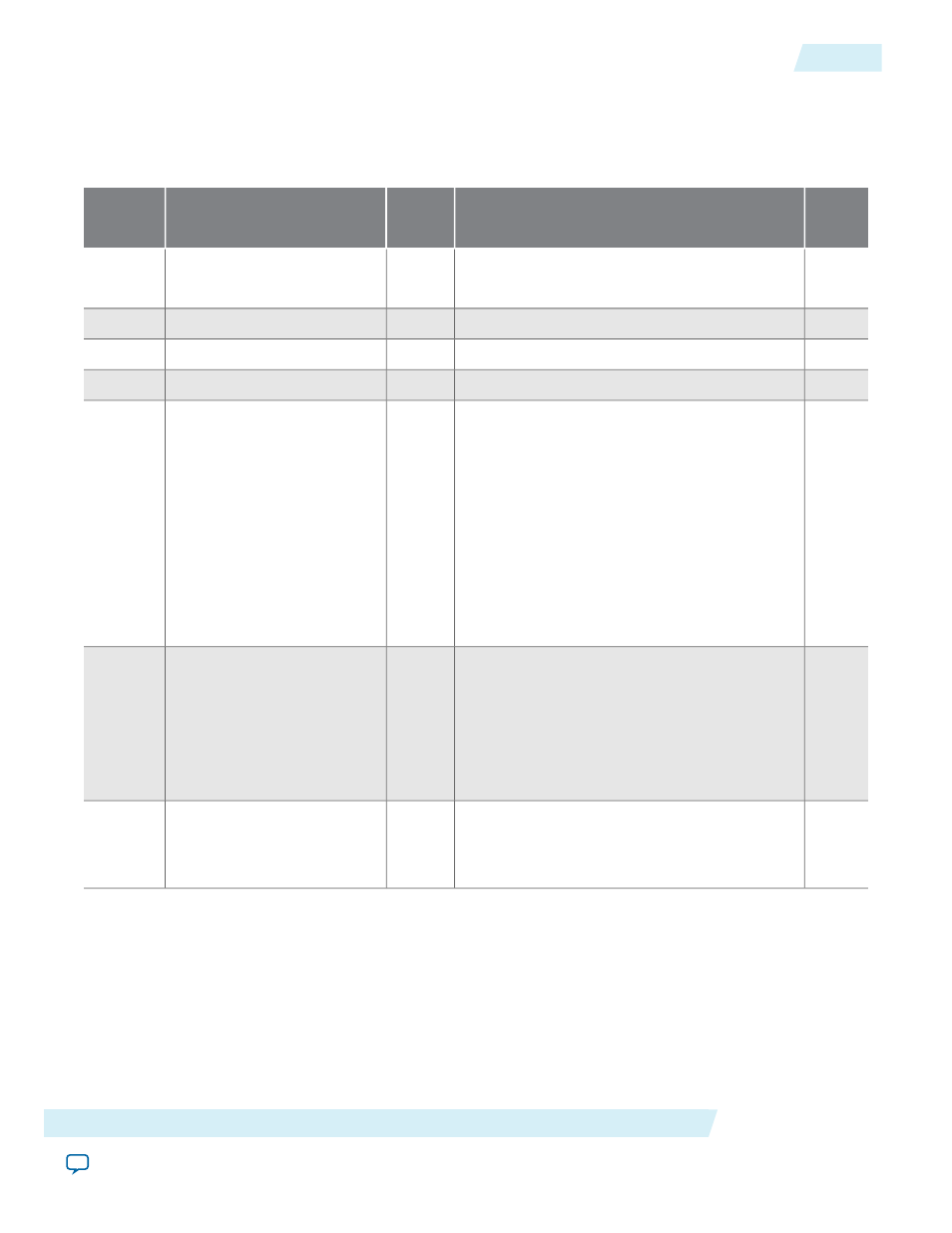

ToD Clock Configuration Register Space

Table C-6: ToD Clock Registers

HW

Reset

Description

R/W

Name

Dword

Offset

0x0

• Bits 0 to 15: High-order 16-bit second field.

• Bits 16 to 31: Not used.

RW

SecondsH

0x00

0x0

Bits 0 to 32: Low-order 32-bit second field.

RW

SecondsL

0x01

0x0

Bits 0 to 32: 32-bit nanosecond field.

RW

NanoSec

0x02

—

Reserved for future use

—

Reserved

0x03

n

The period for the frequency adjustment.

• Bits 0 to 15: Period in fractional nanosecond

(

PERIOD_FNS

).

• Bits 16 to 24: Period in nanosecond (

PERIOD_

NS

).

• Bits 25 to 31: Not used.

The default value for the period depends on the

f

MAX

of the MAC function. For example, if f

MAX

=

125-MHz, the period is 8-ns (

PERIOD_NS

= 0x0008

and

PERIOD_FNS

= 0x0000).

RW

Period

0x04

0x0

The period for the offset adjustment.

• Bits 0 to 15: Period in fractional nanosecond

(

ADJPERIOD_FNS

).

• Bits 16 to 24: Period in nanosecond

(

ADJPERIOD_NS

).

• Bits 25 to 31: Not used.

RW

AdjustPeriod

0x05

0x06

Bits 0 to 19: The number of AdjustPeriod clock

cycles used during offset adjustment.

Bits 20 to 31: Not used.

RW

AdjustCount

0x06

Altera Corporation

Time-of-Day (ToD) Clock

C-5

ToD Clock Configuration Register Space

UG-01008

2014.06.30