Altera Triple Speed Ethernet MegaCore Function User Manual

Page 97

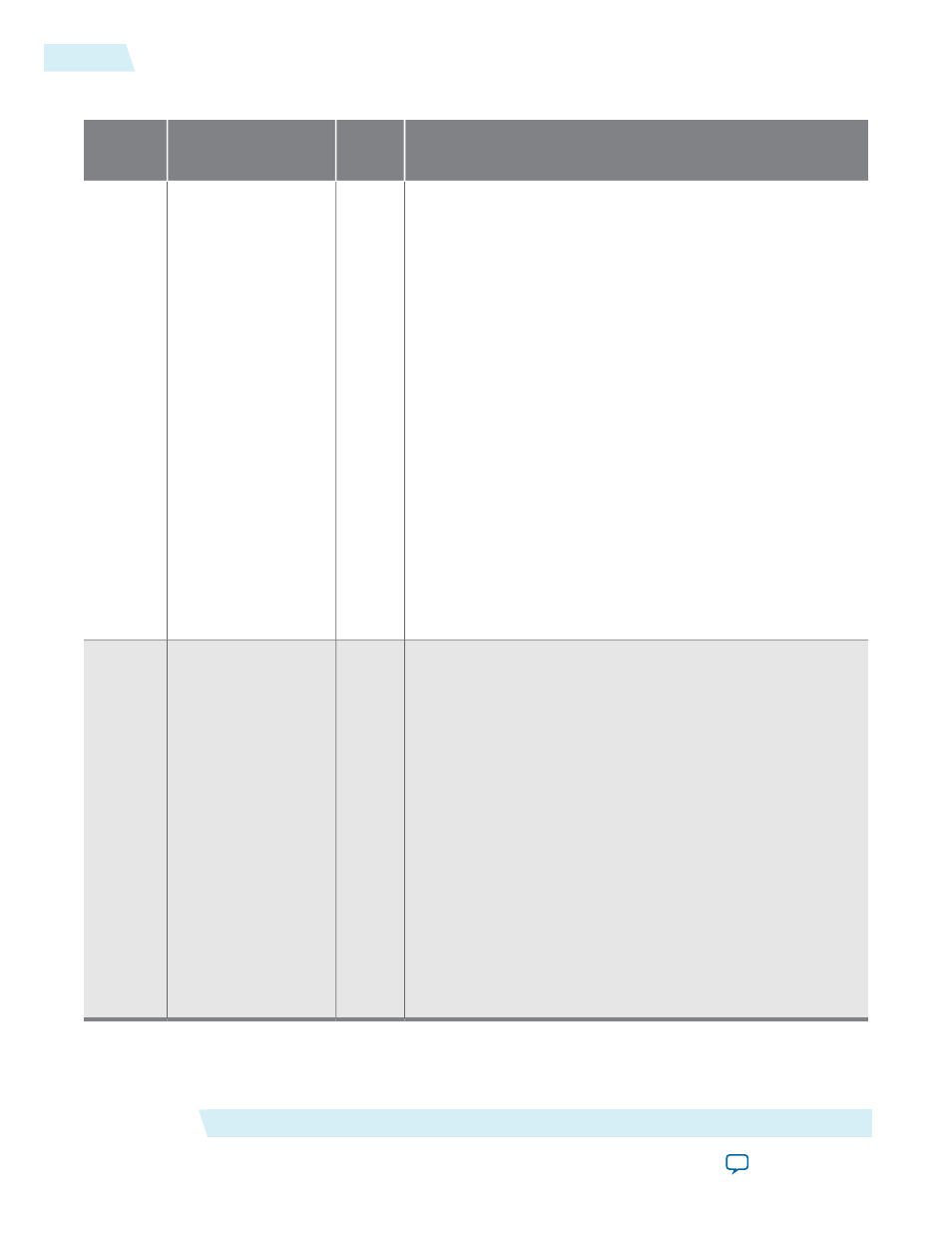

Table 6-5: Transmit and Receive Command Registers

Description

R/W

Name

Dword

Offset

Specifies how the MAC function processes transmit frames.

When you turn on the Align packet headers to 32-bit

boundaries option, this register resets to 0x00040000 upon a

hardware reset. Otherwise, it resets to 0x00.

• Bits 0 to 16—unused.

• Bit 17 (

OMIT_CRC

)—Set this bit to 1 to omit CRC calculation

and insertion on the transmit path. The user application is

therefore responsible for providing the correct data and CRC.

This bit, when set to 1, always takes precedence over the

ff_

tx_crc_fwd

signal.

• Bit 18 (

TX_SHIFT16

)—Set this bit to 1 if the frames from the

user application are aligned on 32-bit boundary. For more

information, refer to

on page 4-5.

This setting applies only when you turn on the Align packet

headers to 32-bit boundary option and in MAC variations

with 32-bit internal FIFO buffers. Otherwise, reading this bit

always return a 0.

In MAC variations without internal FIFO buffers, this bit is

a read-only bit and takes the value of the Align packet

headers to 32-bit boundary option.

• Bits 19 to 31—unused.

RW

tx_cmd_stat

0x3A

Specifies how the MAC function processes receive frames. When

you turn on the Align packet headers to 32-bit boundaries

option, this register resets to 0x02000000 upon a hardware reset.

Otherwise, it resets to 0x00.

• Bits 0 to 24—unused.

• Bit 25 (

RX_SHIFT16

)—Set this bit to 1 to instruct the MAC

function to align receive frames on 32-bit boundary. For more

information on frame alignment, refer to

on page 4-11.

This setting applies only when you turn on the Align packet

headers to 32-bit boundary option and in MAC variations

with 32-bit internal FIFO buffers. Otherwise, reading this bit

always return a 0.

In MAC variations without internal FIFO buffers, this bit is

a read-only bit and takes the value of the Align packet

headers to 32-bit boundary option.

• Bits 26 to 31—unused.

RW

rx_cmd_stat

0x3B

Configuration Register Space

Altera Corporation

UG-01008

Transmit and Receive Command Registers (Dword Offset 0x3A – 0x3B)

6-14

2014.06.30