Programmable 10/100 ethernet, Programmable 10/100/1000 ethernet operation – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 59

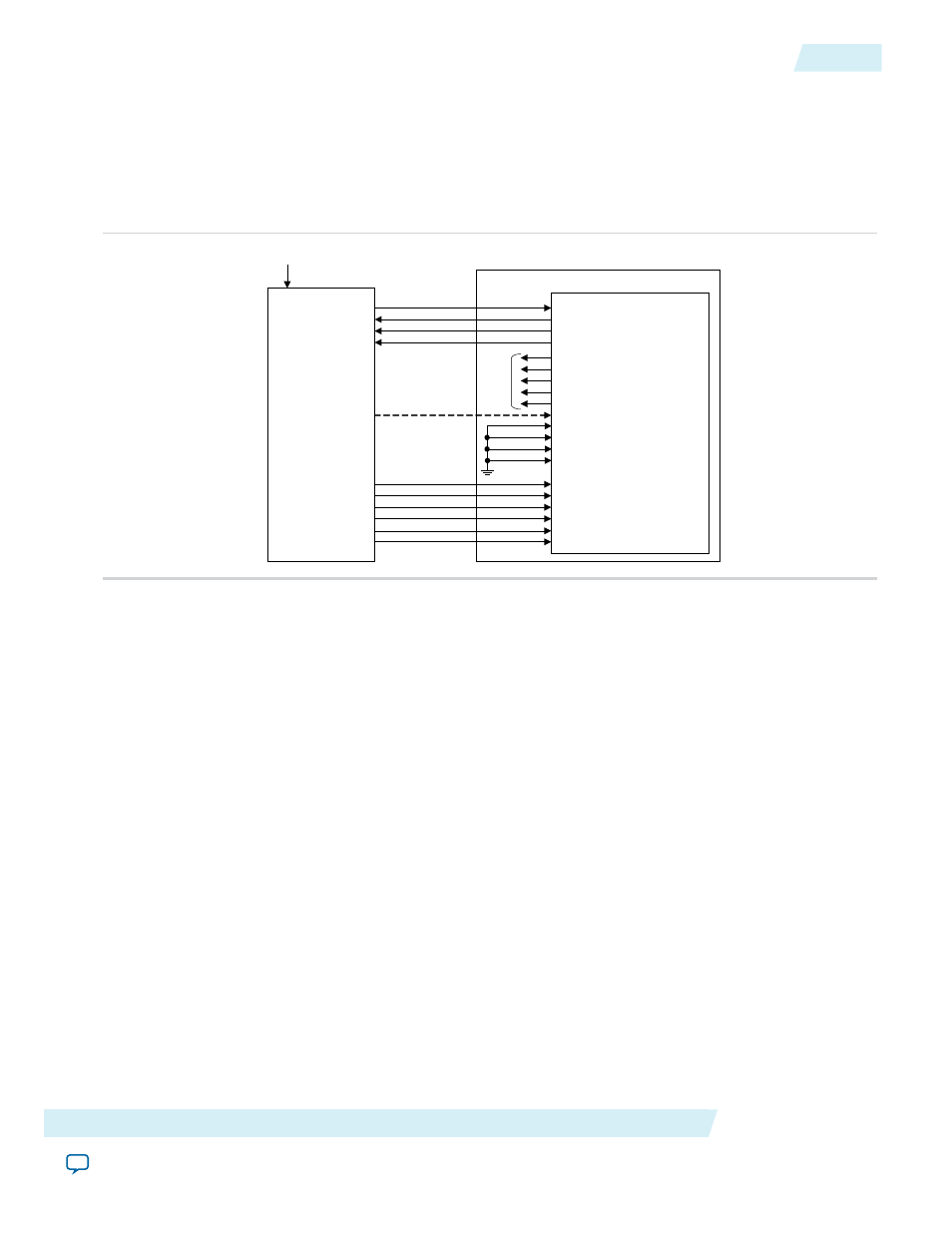

Programmable 10/100 Ethernet

Connect 10/100 Ethernet PHYs to the MAC function via MII. On the receive path, connect the 25-MHz

(100 Mbps) or 2.5-MHz (10 Mbps) clock provided by the PHY device to the MAC clock,

rx_clk

. On the

transmit path, connect the 25 MHz (100 Mbps) or a 2.5 MHz (10 Mbps) clock provided by the PHY to the

MAC clock,

tx_clk

.

Figure 4-11: 10/100 PHY Interface

U

nu

se

d

Altera FPGA

Optional tie to 0

if not used

Reference Clock

25Mhz

ena _10

eth_mode

set _10

set _1000

tx_clk

m_tx_d(3:0)

m_tx_en

m_tx_err

gm_tx_d(7:0)

gm_tx_en

gm_tx_err

rx_clk

m_rx_d(3:0)

m_rx_en

gm_rx_d(7:0)

gm_rx_dv

gm_rx_err

m_rx_err

tx_clk

txd(3:0)

tx_en

tx_err

clk_in/xtali

rx_clk

rxd(3:0)

rx_dv

rx_err

m_rx_col

m_rx_crs

m_rx_col

m_rx_crs

10/100/1000

Ethernet

MAC

10/100

PHY

Programmable 10/100/1000 Ethernet Operation

Typically, 10/100/1000 Ethernet PHY devices implement a shared interface that you connect to a 10/100-Mbps

MAC via MII/RGMII or to a gigabit MAC via GMII/RGMII.

On the receive path, connect the clock provided by the PHY device (2.5 MHz, 25 MHz or 125 MHz) to the

MAC clock,

rx_clk

. The PHY interface is connected to both the MII (active PHY signals) and GMII of the

MAC function.

On the transmit path, standard programmable PHY devices operating in 10/100 mode generate a 2.5 MHz

(10 Mbps) or a 25 MHz (100 Mbps) clock. In gigabit mode, the PHY device expects a 125-MHz clock from

the MAC function. Because the MAC function does not generate a clock output, an external clock module

is introduced to drive the 125 MHz clock to the MAC function and PHY devices. In 10/100 mode, the clock

generated by the MAC to the PHY can be tri-stated.

During transmission, the MAC control signal

eth_mode

selects either MII or GMII. The MAC function

asserts the

eth_mode

signal when the MAC function operates in gigabit mode, which subsequently drives

the MAC GMII to the PHY interface. The

eth_mode

signal is deasserted when the MAC function operates

in 10/100 mode. In this mode, the MAC MII is driven to the PHY interface.

Altera Corporation

Functional Description

4-23

Programmable 10/100 Ethernet

UG-01008

2014.06.30