Tod synchronizer parameter settings – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 209

• 1G master and 10G (312.5 Mhz) slave—(32/63)*125 MHz or (64/315)*312.5 MHz

• 10G (156.25 MHz) master and 10G (312.5 Mhz) slave—(64/63)*156.25 MHz or (32/63)*312.5 MHz

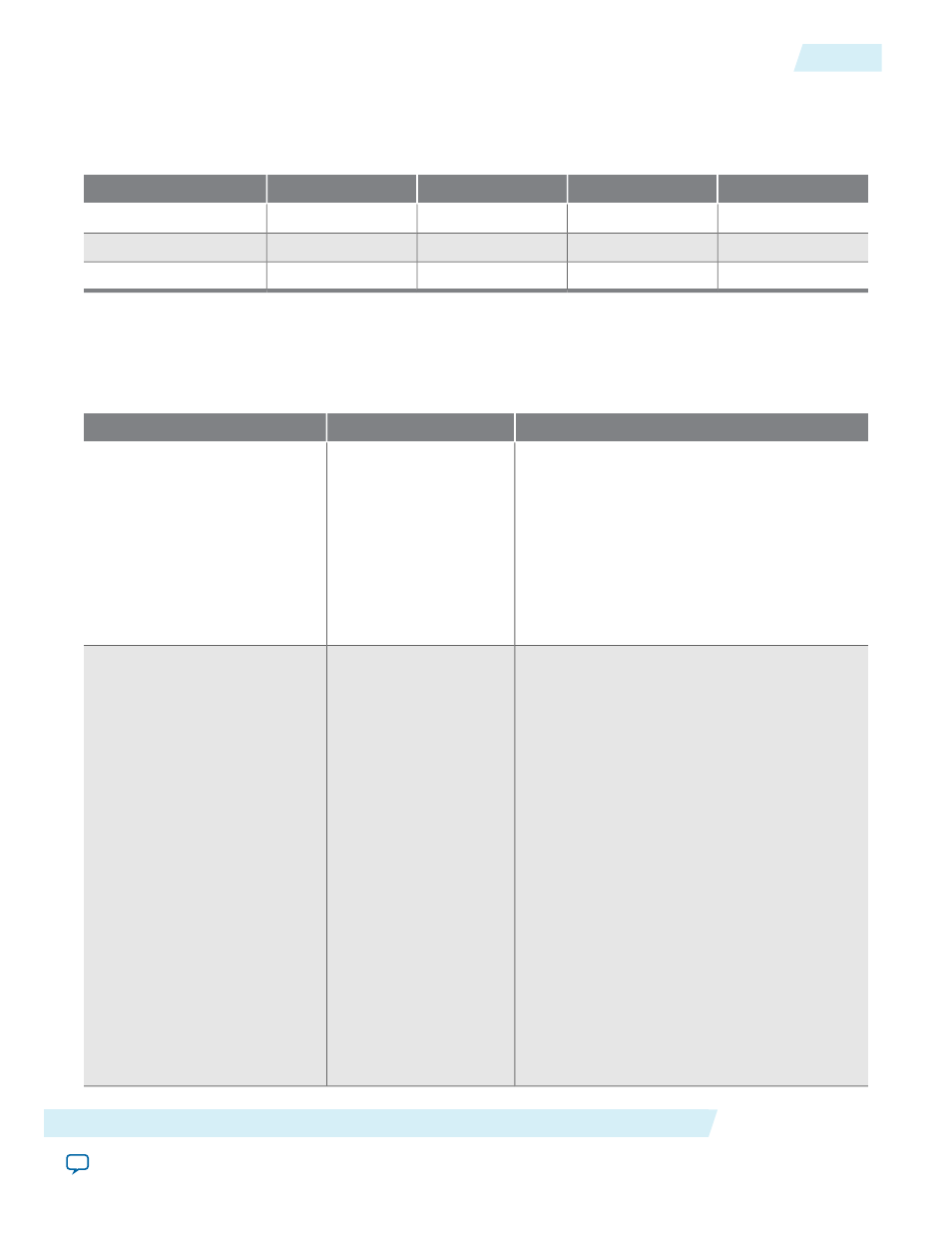

Table D-1: Settings to Achieve The Recommended Factors for Stratix V PLL

32/63

64/315

16/63

64/63

Settings

32

64

16

64

M-Counter

03

21

03

21

N-Counter

21

15

21

03

C-Counter

ToD Synchronizer Parameter Settings

Table D-2: ToD Synchronizer Configuration Parameters

Description

Value

Name

Value that defines the time of day format that

this block is synchronizing.

The default value is 1.

• 1: 96-bits format (32 bits seconds, 48 bits

nanosecond and 16 bits fractional

nanosecond)

• 0: 64-bits format (48 bits nanosecond and 16

bits fractional nanoseconds).

Between 0 and 1

TOD_MODE

Value that defines types of synchronization.

The default value is 1.

• 0: Master clock frequency is 125MHz (1G)

while slave is 156.25MHz (10G).

• 1: Master clock frequency is 156.25MHz

(10G) while slave is 125MHz (1G).

• 2: Master and slave are same in the same

frequency; can be in different ppm or phase.

When you select this mode, specify the

period of master and slave through the

PERIOD_NSEC

and

PERIOD_FNSEC

parameters.

• 3: Master clock frequency is 156.25MHz

(10G) while slave is 312.5MHz (10G).

• 4: Master clock frequency is 312.5MHz (10G)

while slave is 156.25MHz (10G).

• 5: Master clock frequency is 125MHz (1G)

while slave is 312.5MHz (10G).

• 6: Master clock frequency is 312.5MHz (10G)

while slave is 125MHz (1G).

Between 0 and 6

SYNC_MODE

Altera Corporation

ToD Synchronizer

D-3

ToD Synchronizer Parameter Settings

UG-01008

2014.06.30