Design implementation, Design implementation -1 – Altera Arria 10 Avalon-MM User Manual

Page 141

Design Implementation

11

2015.05.14

UG-01145_avmm

Completing your design includes additional steps to specify analog properties, pin assignments, and

timing constraints.

Making Pin Assignments to Assign I/O Standard to Serial Data Pins

Before running Quartus II compilation, use the Pin Planner to assign I/O standards to the pins of the

device.

1. On the Quartus II Assignments menu, select Pin Planner.

The Pin Planner appears.

2. In the Node Name column, locate the PCIe serial data pins.

3. In the I/O Standard column, double-click the right-hand corner of the box to bring up a list of

available I/O standards.

4. Select the appropriate standard from the following table.

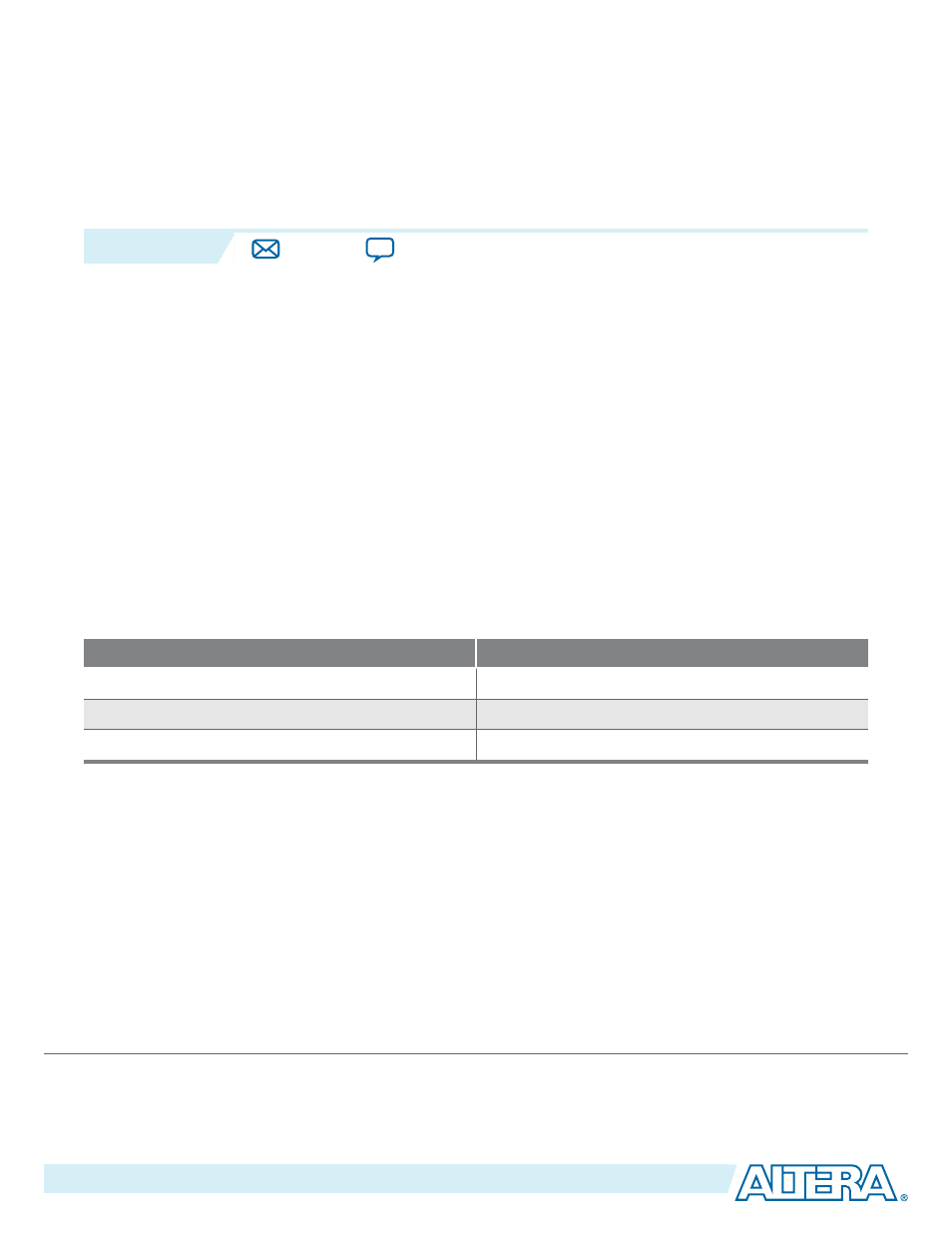

Table 11-1: I/O Standards for HSSI Pins

Pin Type

I/O Standard

HSSI REFCLK

Current Mode Logic (CML), HCSL

HSSI RX

Current Mode Logic (CML)

HSSI TX

High Speed Differential I/O

The Quartus II software adds instance assignments to your Quartus II Settings File (

*.qsf

). The assignment

is in the form

set_instance_assignment -name IO_STANDARD <"IO_STANDARD_NAME"> -to

<signal_name>

. The

*.qsf

is in your synthesis directory.

Related Information

Recommended Reset Sequence to Avoid Link Training Issues

Successful link training can only occur after the FPGA is configured. Designs using CvP for configuration

initially load the I/O ring and periphery image. Arria 10 devices include a Nios II Hard Calibration IP

core that automatically calibrates transceivers to optimize signal quality after CvP completes and before

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134