Altera Arria 10 Avalon-MM User Manual

Page 51

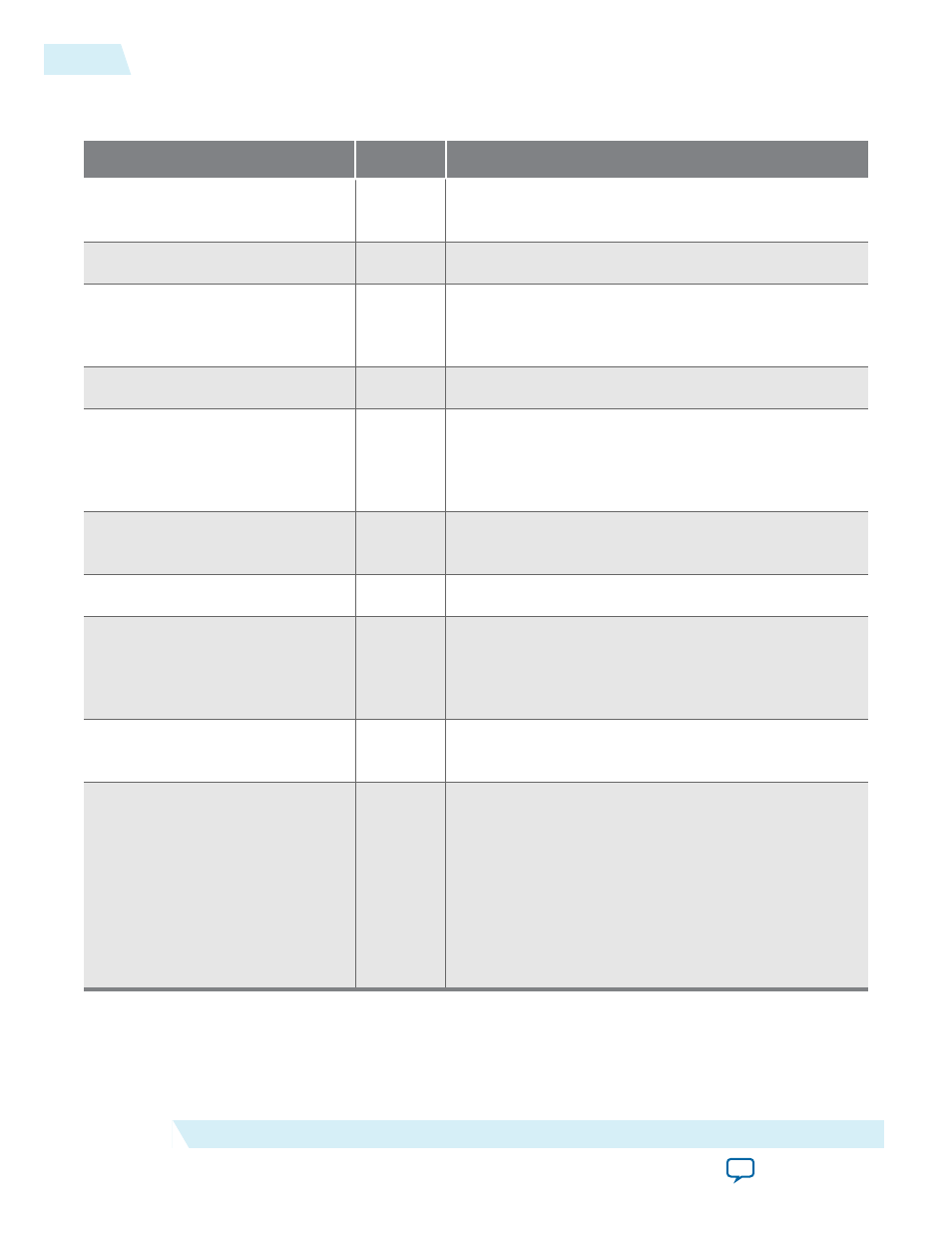

Table 5-2: Avalon-MM RX Master Interface Signals

Signals that include Bar number 0 also exist for BAR1–BAR5 when additional BARs are enabled.

Signal Name

Direction

Description

RxmWrite<n>

Output

Asserted by the core to request a write to an Avalon-

MM slave.

RxmAddress_<n>_o[31:0]

Output

The address of the Avalon-MM slave being accessed.

RxmWriteData_<n>_o[<w>-1:0]

Output

RX data being written to slave. <w> = 64 or 128 for the

full-featured IP core. <w> = 32 for the completer-only

IP core.

RxmByteEnable_<n>_o[<w>-1:0]

Output

Byte enable for write data.

RXMBurstCount_<n>_o[6 or

5:0]

Output

The burst count, measured in qwords, of the RX write or

read request. The width indicates the maximum data

that can be requested. The maximum data in a burst is

512 bytes.

RXMWaitRequest_<n>_o

Input

Asserted by the external Avalon-MM slave to hold data

transfer.

RXMRead_<n>_o

Output

Asserted by the core to request a read.

RXMReadData_<n>_o[<w>-1:0]

Input

Read data returned from Avalon-MM slave in response

to a read request. This data is sent to the IP core through

the TX interface. <w> = 64 or 128 for the full-featured

IP core. <w> = 32 for the completer-only IP core.

RXMReadDataValid_<n>_i

Input

Asserted by the system interconnect fabric to indicate

that the read data on is valid.

RxmIrq_<n>[<m>:0]

,

<m>< 16

Input

Indicates an interrupt request asserted from the system

interconnect fabric. This signal is only available when

the CRA port is enabled. Qsys-generated variations have

as many as 16 individual interrupt signals (<m>≤15). If

rxm_irq_<n>[<m>:0]

is asserted on consecutive cycles

without the deassertion of all interrupt inputs, no MSI

message is sent for subsequent interrupts. To avoid

losing interrupts, software must ensure that all interrupt

sources are cleared for each MSI message received.

The following figure illustrates the RX master port propagating requests to the Application Layer and also

shows simultaneous, DMA read and write activity

5-4

RX Avalon-MM Master Signals

UG-01145_avmm

2015.05.14

Altera Corporation

64- or 128-Bit Avalon-MM Interface to the Application Layer