Hard ip reconfiguration interface, Hard ip reconfiguration interface -11 – Altera Arria 10 Avalon-MM User Manual

Page 58

Signal

Direction

Description

IntxAck_o

Output

This signal is the acknowledge for

IntxReq_i

. It is asserted for at

least one cycle either when either of the following events occur:

• The

Assert_INTA

message TLP has been transmitted in

response to the assertion of the

IntxReq_i

.

• The

Deassert_INTA

message TLP has been transmitted in

response to the deassertion of the

IntxReq_i

signal.

Refer to the timing diagrams below.

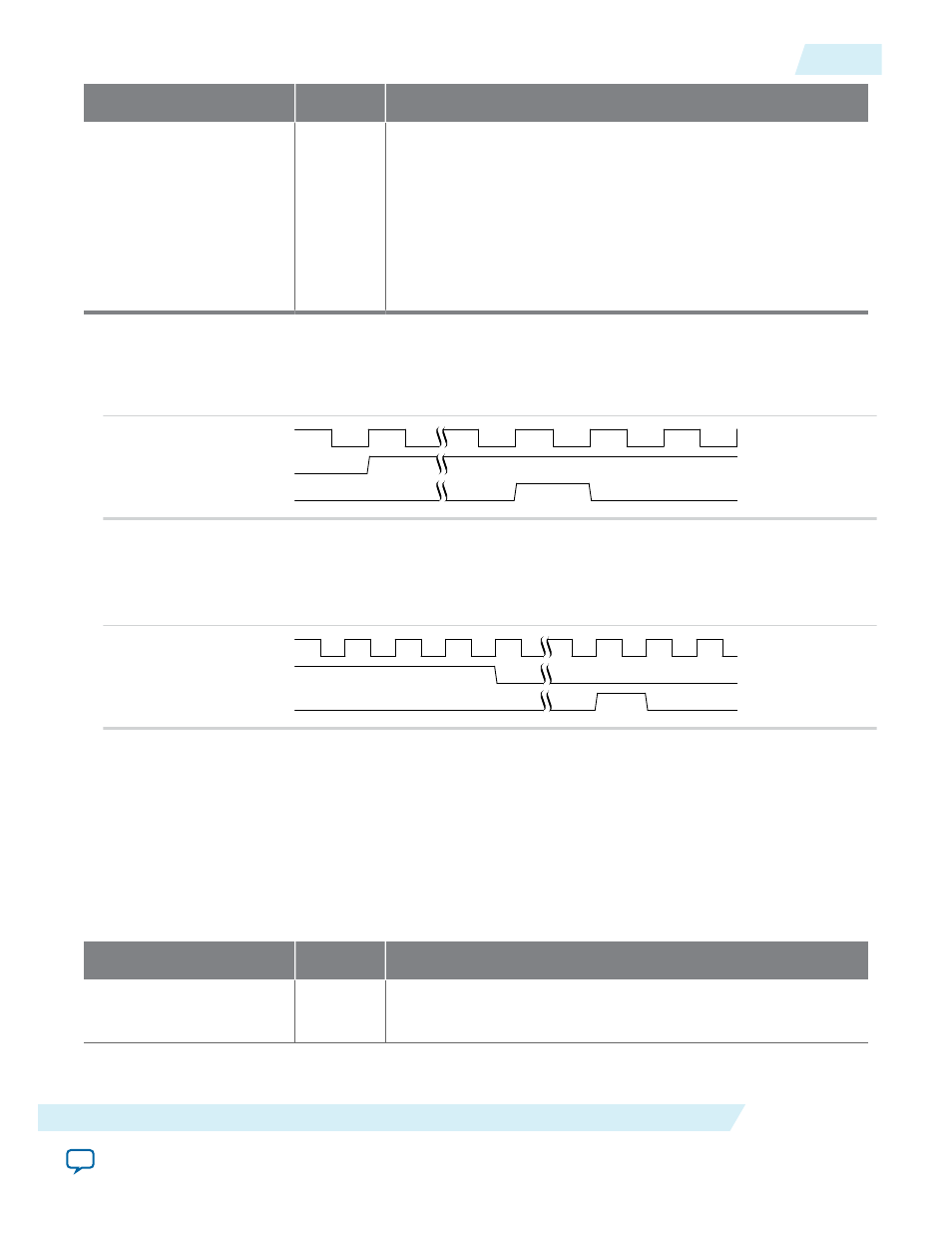

The following figure illustrates interrupt timing for the legacy interface. In this figure the assertion of

IntxReq_i

instructs the Hard IP for PCI Express to send an

Assert_INTA

message TLP.

Figure 5-4: Legacy Interrupt Assertion

clk

IntxReq_i

IntAck_o

The following figure illustrates the timing for deassertion of legacy interrupts. The assertion of

IntxReq_i

instructs the Hard IP for PCI Express to send a

Deassert_INTA

message.

Figure 5-5: Legacy Interrupt Deassertion

clk

IntxReq_i

IntAck_o

Hard IP Reconfiguration Interface

The Hard IP reconfiguration interface is an Avalon-MM slave interface with a 10-bit address and 16-bit

data bus. You can use this bus to dynamically modify the value of configuration registers that are read-

only at run time. To ensure proper system operation, reset or repeat device enumeration of the PCI

Express link after changing the value of read-only configuration registers of the Hard IP.

Table 5-7: Hard IP Reconfiguration Signals

Signal

Direction

Description

hip_reconfig_clk

Input

Reconfiguration clock. The frequency range for this clock is 100–

125 MHz.

UG-01145_avmm

2015.05.14

Hard IP Reconfiguration Interface

5-11

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation