Altera Arria 10 Avalon-MM User Manual

Page 208

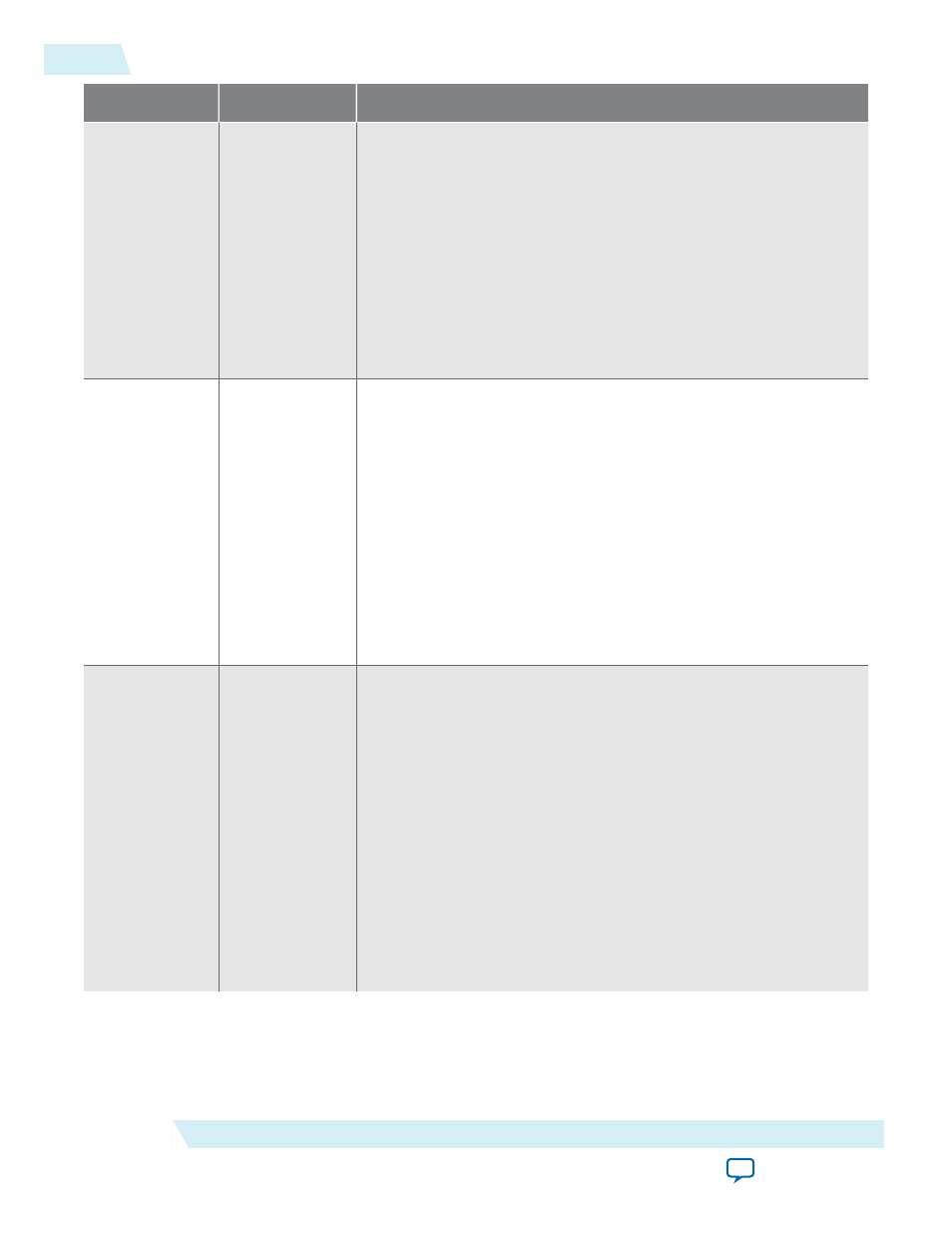

Date

Version

Changes Made

• Removed list of static example designs from

page 1-9. You can derive the list from the installation directory

where example designs are available.

• Removed Migration and TLP Format appendices, and added new

on page 16-1.

on page 15-1 and

on page 14-49. Removed Reducing Counter Values for

Serial Simulations section, which is no longer relevant. Default

counter values are automatically set for simulation.

• Updated information in

• Fixed minor errors and typos.

2014.12.15

14.1

Made the following changes:

• Revised Root Port programming model description, Receiving a

Completion TLP, to cover read and non-posted completions.

• Added Avalon-MM Testbench and Design Example chapter.

• Added statement that the bottom left hard IP block includes the

CvP functionality for flip chip packages. For other package types,

the CvP functionality is in the bottom right block.

• Corrected bit definitions for CvP Status register.

• Updated definition of

CVP_NUMCLKS

in the CvP Mode Control

register.

• Added definitions for

test_in[2]

,

test_in[6]

, and

test_in[7]

.

• Revised discussion of SDC files to include in Quartus II project.

2014.08.18

14.0 Arria 10

Made the following changes to the Arria 10 Avalon-MM Hard IP for

PCI Express

• Optionally changed the

cra_address

to 14 bits from 12.

• Added simulation log file,

altpcie_monitor_a10_dlhip_tlp_file_

log.log

, that is automatically generated in your simulation

directory. To simulate in the Quartus II 14.0 software release, you

must regenerate your IP core to create the supporting monitor file

the generates

altpcie_monitor_a10_dlhip_tlp_file_log.log

. Refer to

Understanding Simulation Dump File Generation for details.

• Added support for 64-bit addressing, making address translation

unnecessary.

• Removed Channel Placement for PCIe in Arria 10 Devices. Please

contact your Altera sales representative for PLL and channel

usage.

C-2

Revision History for the Avalon-MM Interface

UG-01145_avmm

2015.05.14

Altera Corporation

Additional Information