Altera Arria 10 Avalon-MM User Manual

Page 96

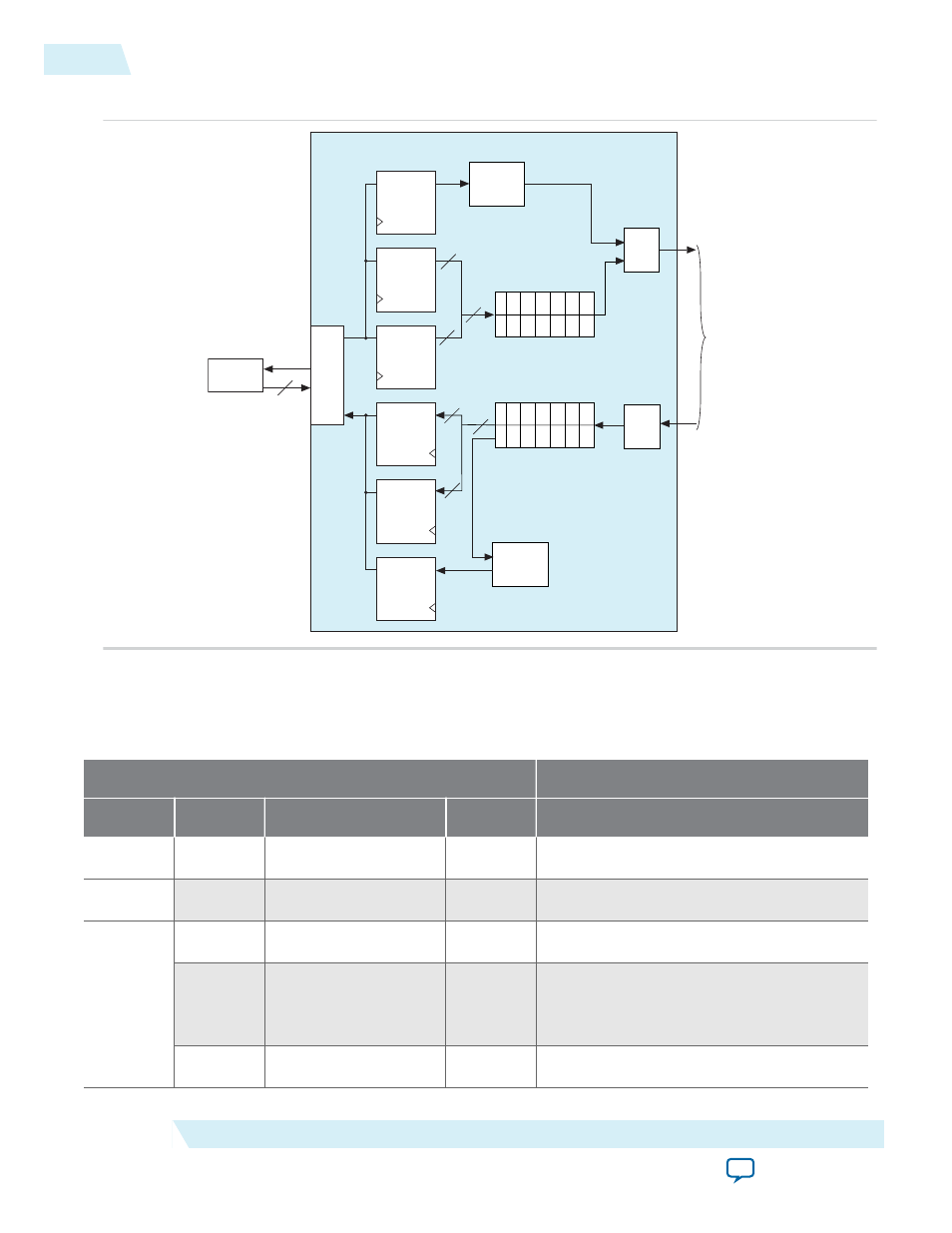

Figure 6-12: Root Port TLP Data Registers

RX_TX_CNTL

RP_RXCPL_

REG0

RP_RXCPL_

REG1

RP_RXCPL_

STATUS

Control

Register

Access

Slave

Avalon-MM

Master

32

32

32

32

64

64

32

IRQ

RP TX

CTRL

TX

CTRL

RP_TX_FIFO

RP CPL

CTRL

RX

CTRL

RP_RXCPL_FIFO

TLP Direct Channel

to Hard IP for PCIe

Root-Port TLP Data Registers

Avalon-MM Bridge -

RX_TX_Reg1

RP_TX_Reg0

Note: The high performance TLPs implemented by Avalon-MM ports in the Avalon-MM Bridge are also

available for Root Ports. For more information about these TLPs, refer to Avalon-MM Bridge TLPs.

Table 6-26: Root Port TLP Data Registers, 0x2000–0x2FFF

Root-Port Request Registers

Address Range: 0x2800-0x2018

Address

Bits

Name

Access

Description

0x2000

[31:0]

RP_TX_REG0

W

Lower 32 bits of the TX TLP.

0x2004

[31:0]

RP_TX_REG1

W

Upper 32 bits of the TX TLP.

0x2008

[31:2]

Reserved

—

—

[1]

RP_TX_CNTRL.EOP

W

Write 1’b1 to specify the of end a packet.

Writing this bit frees the corresponding

entry in the FIFO.

[0]

RP_TX_CNTRL.SOP

W

Write 1’b1 to specify the start of a packet.

6-30

Root Port TLP Data Registers

UG-01145_avmm

2015.05.14

Altera Corporation

Registers