Test signals, Test signals -19 – Altera Arria 10 Avalon-MM User Manual

Page 66

Test Signals

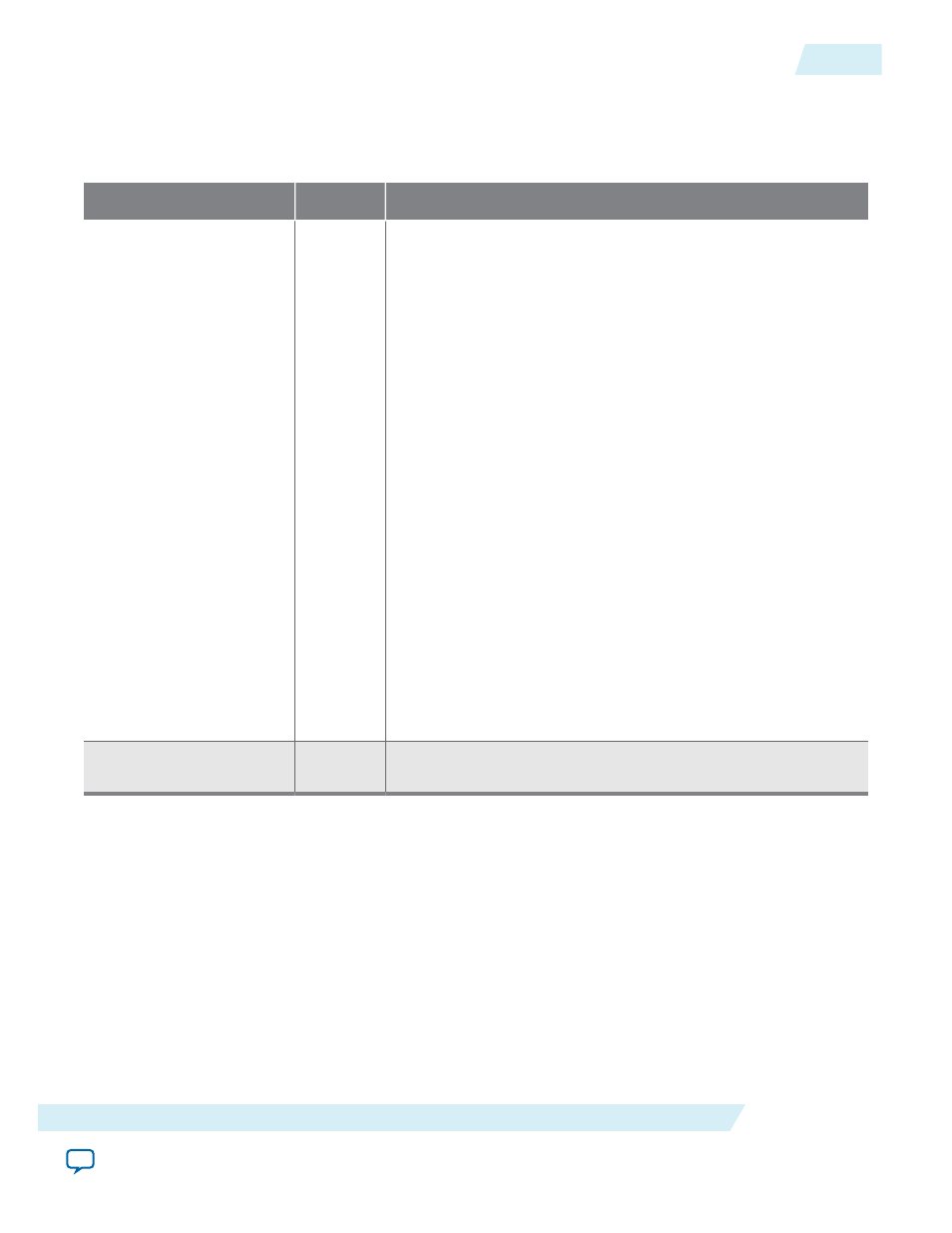

Table 5-10: Test Interface Signals

The

test_in

bus provides run-time control and monitoring of the internal state of the IP core.

Signal

Direction

Description

test_in[31:0]

Input

The bits of the

test_in

bus have the following definitions:

• [0]: Simulation mode. This signal can be set to 1 to accelerate

initialization by reducing the value of many initialization

counters.

• [1]: Reserved. Must be set to 1’b0.

• [2]: Descramble mode disable. This signal must be set to 1

during initialization in order to disable data scrambling. You

can use this bit in simulation for both Endpoints and Root

Ports to observe descrambled data on the link. Descrambled

data cannot be used in open systems because the link partner

typically scrambles the data.

• [4:3]: Reserved. Must be set to 4’b01.

• [5]: Compliance test mode. Disable/force compliance mode.

When set, prevents the LTSSM from entering compliance

mode. Toggling this bit controls the entry and exit from the

compliance state, enabling the transmission of Gen1, Gen2

and Gen3 compliance patterns.

• [6]: Forces entry to compliance mode when a timeout is

reached in the polling.active state and not all lanes have

detected their exit condition.

• [7]: Disable low power state negotiation. Altera recommends

setting thist bit.

• [31:8]: Reserved. Set to all 0s.

simu_mode_pipe

Input

When asserted, simulation operates in parallel mode. When

deasserted the simulation is serial.

UG-01145_avmm

2015.05.14

Test Signals

5-19

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation