Uncorrectable internal error mask register, Uncorrectable internal error mask register -31 – Altera Arria 10 Avalon-MM User Manual

Page 97

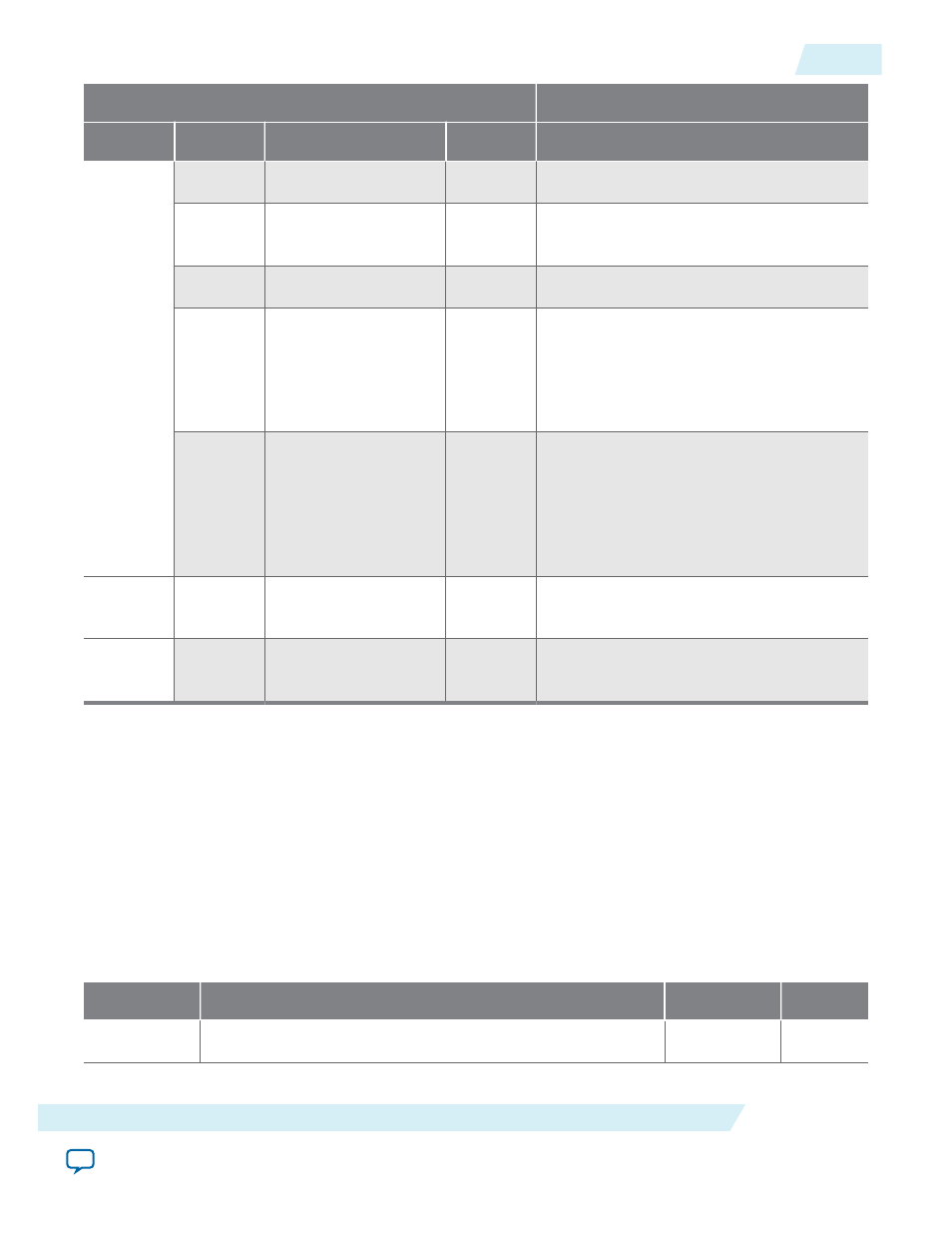

Root-Port Request Registers

Address Range: 0x2800-0x2018

Address

Bits

Name

Access

Description

0x2010

[31:16]

Reserved

—

—

[15:8]

RP_RXCPL_STATUS

R

Specifies the number of words in the RX

completion FIFO that contain valid data.

[7:2]

Reserved

—

—

[1]

RP_RXCPL_STATUS.EOP

R

When 1’b1, indicates that the data for a

Completion TLP is ready to be read by the

Application Layer. The Application Layer

must poll this bit to determine when a

Completion TLP is available.

[0]

RP_RXCPL_STATUS.SOP

R

When 1’b1, indicates that the final data for

a Completion TLP is ready to be read by

the Application Layer. The Application

Layer must poll this bit to determine when

the final data for a Completion TLP is

available.

0x2014

[31:0]

RP_RXCPL_REG0

RC

Lower 32 bits of a Completion TLP.

Reading frees this entry in the FIFO.

0x2018

[31:0]

RP_RXCPL_REG1

RC

Upper 32 bits of a Completion TLP.

Reading frees this entry in the FIFO.

Related Information

Uncorrectable Internal Error Mask Register

Table 6-27: Uncorrectable Internal Error Mask Register

The

Uncorrectable Internal Error Mask

register controls which errors are forwarded as internal

uncorrectable errors. With the exception of the configuration error detected in CvP mode, all of the errors are

severe and may place the device or PCIe link in an inconsistent state. The configuration error detected in CvP

mode may be correctable depending on the design of the programming software. The access code RWS stands for

Read Write Sticky meaning the value is retained after a soft reset of the IP core.

Bits

Register Description

Reset Value

Access

[31:12]

Reserved.

1b’0

RO

UG-01145_avmm

2015.05.14

Uncorrectable Internal Error Mask Register

6-31

Registers

Altera Corporation