Altera Arria 10 Avalon-MM User Manual

Page 153

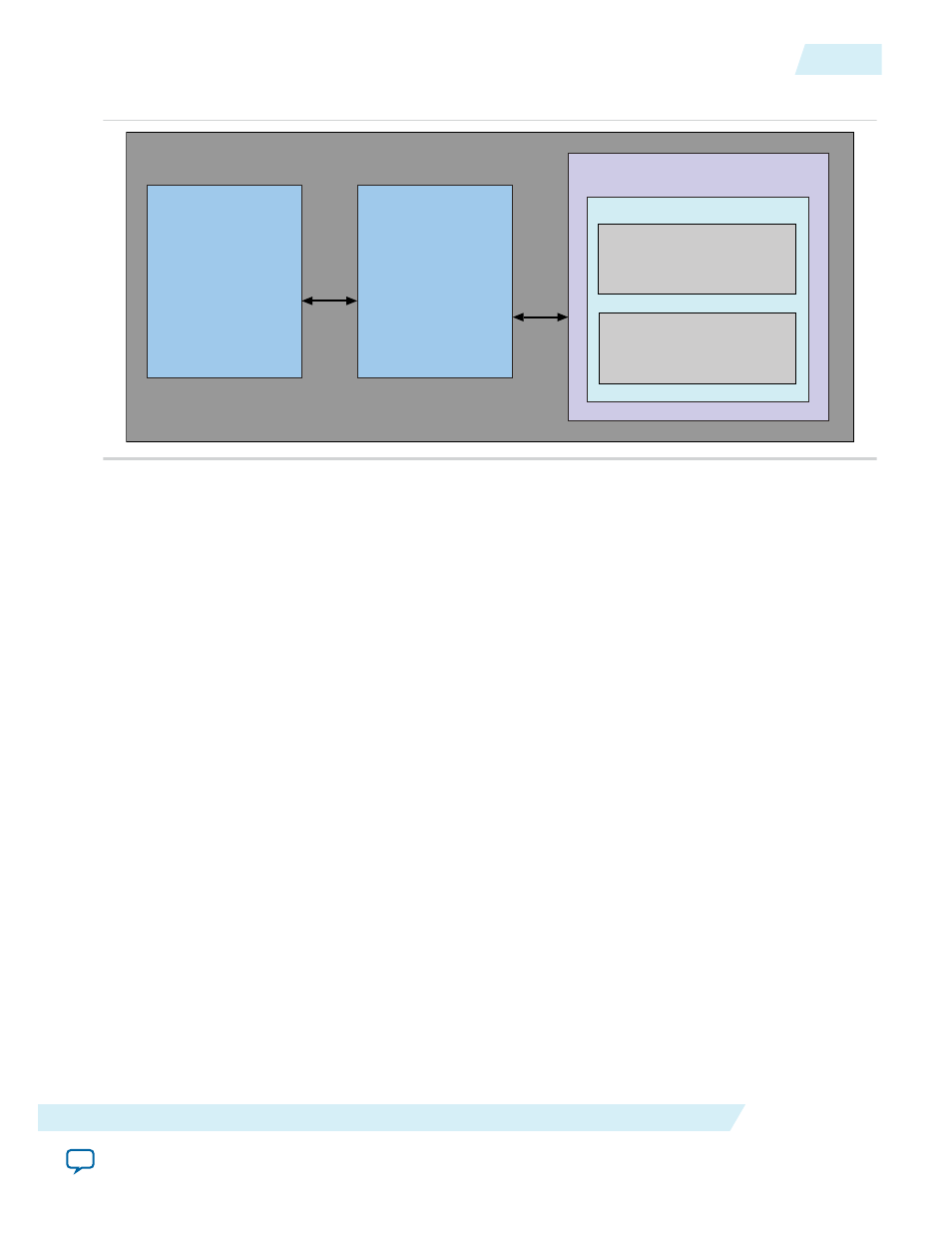

Figure 14-1: Design Example for Endpoint Designs

APP

Hard IP for PCI Express Testbench for Endpoints

Avalon-MM

reset

Avalon-MM

reset

DUT

<instance_name>_altera_

pcie_a10_hip_<version>_

<generated_string>.v

Root Port Model

altpcie_<dev>_tbed_hwtcl.c

altpcietb_bfm_top_rp

PIPE or

Serial

Interface

Root Port BFM

altpcietb_bfm_rp_gen3_x8

Root Port Driver and Monitor

altpcietb_bfm_driver_avmm

altera_avalon_dma.v

The top-level of the testbench instantiates the following main modules:

• <qsys_systemname>— This is the example Endpoint design. For more information about this module,

refer to DMA Design Examples.

• altpcie_a10_tbed_hwtcl.v—This is the Root Port PCI Express BFM. For more information about this

module, refer to Root Port BFM.

• altera_avalon_dma—This module drives transactions to the Root Port BFM. This is the module that

you modify to vary the transactions sent to the example Endpoint design or your own design. For

more information about this module, refer to Root Port Design Example.

In addition, the testbench has routines that perform the following tasks:

• Generates the reference clock for the Endpoint at the required frequency.

• Provides a PCI Express reset at start up.

Note: Before running the testbench, you should set the following parameters in

<instantiation_name>_tb/

sim/<instantiation_name>_tb.v

:

•

serial_sim_hwtcl

: Set to 1 for serial simulation and 0 for PIPE simulation.

•

enable_pipe32_phyip_ser_driver_hwtcl

: Set to 0 for serial simulation and 1 for PIPE

simulation.

Related Information

Getting Started with the Avalon-MM Arria 10 Hard IP for PCI Express

on page 2-1

UG-01145_avmm

2015.05.14

Arria 10 Avalon-MM Endpoint Testbench

14-3

Avalon-MM Testbench and Design Example

Altera Corporation