Altera Arria 10 Avalon-MM User Manual

Page 46

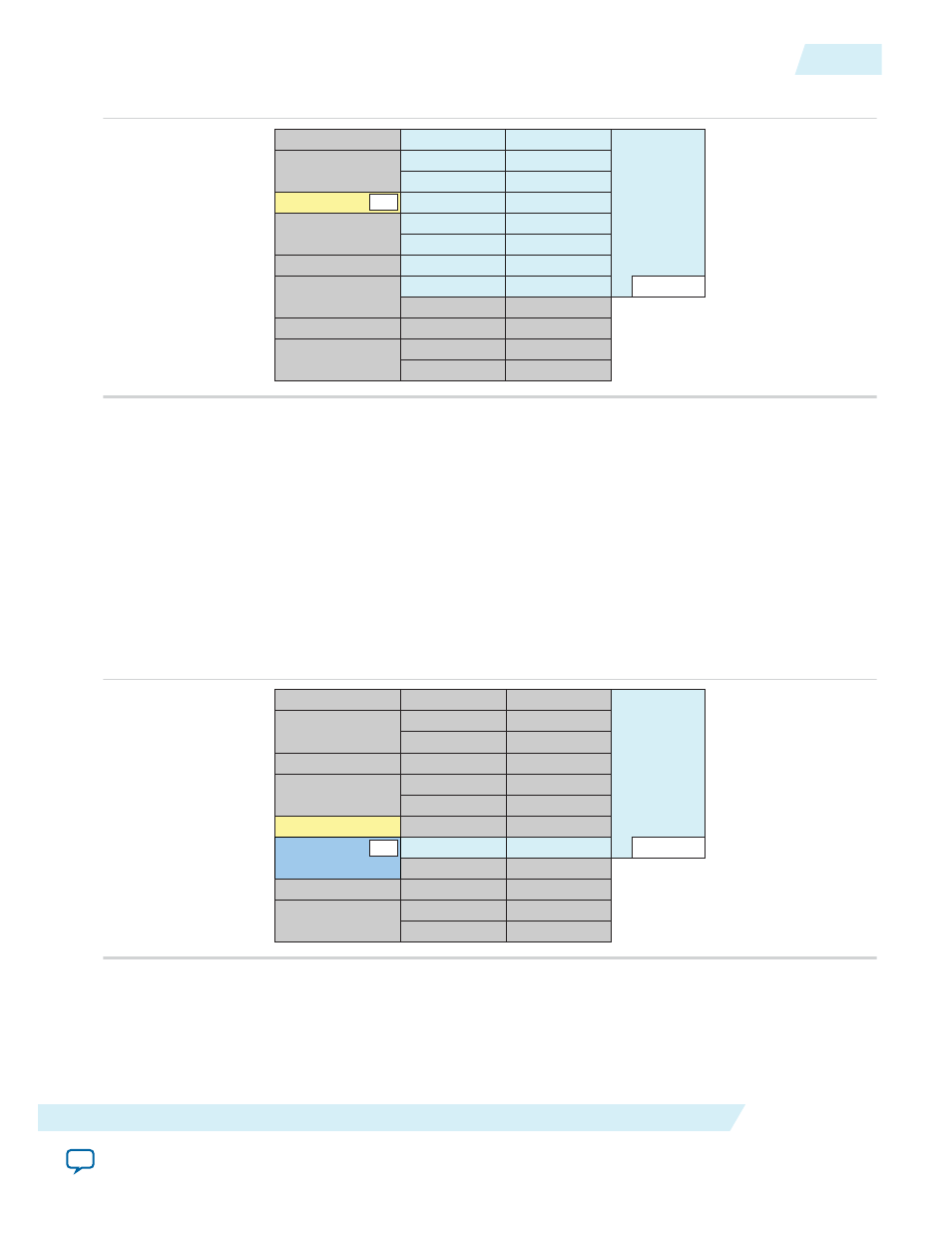

Figure 4-11: Gen1 and Gen2 x8 Channel Placement

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 0

PMA Channel 3

PMA Channel 2

PMA Channel 1

PMA Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 0

PCS Channel 3

PCS Channel 2

PCS Channel 1

PCS Channel 0

Hard IP

for PCIe

Hard IP Ch0

PMA Channel 1

PCS Channel 1

PMA Channel 4

PCS Channel 4

PMA Channel 5

PCS Channel 5

PMA Channel 2

PCS Channel 2

fPLL1

ATX1 PLL

ATX0 PLL

ATX1 PLL

fPLL0

ATX0 PLL

fPLL1

fPLL0

Master

CGB

Master

CGB

indicates the location of the master clock generation block (CGB)

Channel Placement and fPLL and ATX PLL Usage for the Gen3 Data Rate

The following figures illustrate the x1, x2, x4, and x8 channel placement for the Arria 10 Hard IP for PCI

Express. Gen3 variants must initially train at the Gen1 data rate. Consequently, Gen3 variants require an

fPLL to generate the 2.5 and 5.0 Gbps clocks, and an ATX PLL to generate the 8.0 Gbps clock.

In these figures, channels that are not used for the PCI Express protocol are available for other protocols.

Unused channels are shown in gray.

Note: In all configurations, physical channel 4 in the PCS connects to logical channel 0 in the hard IP.

You cannot change the channel placements illustrated below.

Figure 4-12: Arria 10 Gen3 x1 Channel Placement

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 0

PMA Channel 4

PMA Channel 3

PMA Channel 2

PMA Channel 1

PMA Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 0

PCS Channel 4

PCS Channel 3

PCS Channel 2

PCS Channel 1

PCS Channel 0

Hard IP

for PCIe

fPLL1

ATX1 PLL

fPLL0

ATX0 PLL

fPLL0

ATX0 PLL

Hard IP Ch0

PMA Channel 1

PCS Channel 1

PMA Channel 2

PCS Channel 2

PMA Channel 5

PCS Channel 5

fPLL1

ATX1 PLL

Master

CGB

Master

CGB

indicates the location of the master clock generation block (CGB)

UG-01145_avmm

2015.05.14

Channel Placement and fPLL and ATX PLL Usage for the Gen3 Data Rate

4-7

Physical Layout of Hard IP In Arria 10 Devices

Altera Corporation