Altera Arria 10 Avalon-MM User Manual

Page 94

Sending a Read TLP or Receiving a Non-Posted Completion TLP

The TLPs associated with the Non-Posted TX requests are stored in the RP_RX_CPL FIFO buffer and

subsequently loaded into RP_RXCPL registers. The Application Layer performs the following sequence to

retrieve the TLP.

1. Polls the

RP_RXCPL_STA

TUS.SOP

to determine when it is set to 1’b1.

2. Then

RP_RXCPL_STATUS.SOP

= 1’b’1, reads

RP_RXCPL_REG0

and

RP_RXCPL_REG1

to retrieve dword 0

and dword 1 of the TLP.

3. Read the

RP_RXCPL_STATUS.EOP.

• If

RP_RXCPL_STATUS.EOP =

1’b0, read

RP_RXCPL_REG0

and

RP_RXCPL_REG1

to retrieve dword 2

and dword 3 of the TLP, then repeat step 3.

• If

RP_RXCPL_STATUS.EOP =

1’b1, read

RP_RXCPL_REG0

and

RP_RXCPL_REG1

to retrieve final

dwords of TLP.

PCI Express to Avalon-MM Interrupt Status and Enable Registers for Root Ports

The Root Port supports MSI, MSI-X and legacy (INTx) interrupts. MSI and MSI-X interrupts are memory

writes from the Endpoint to the Root Port. MSI and MSI-X requests are forwarded to the interconnect

without asserting

CraIrq_o

.

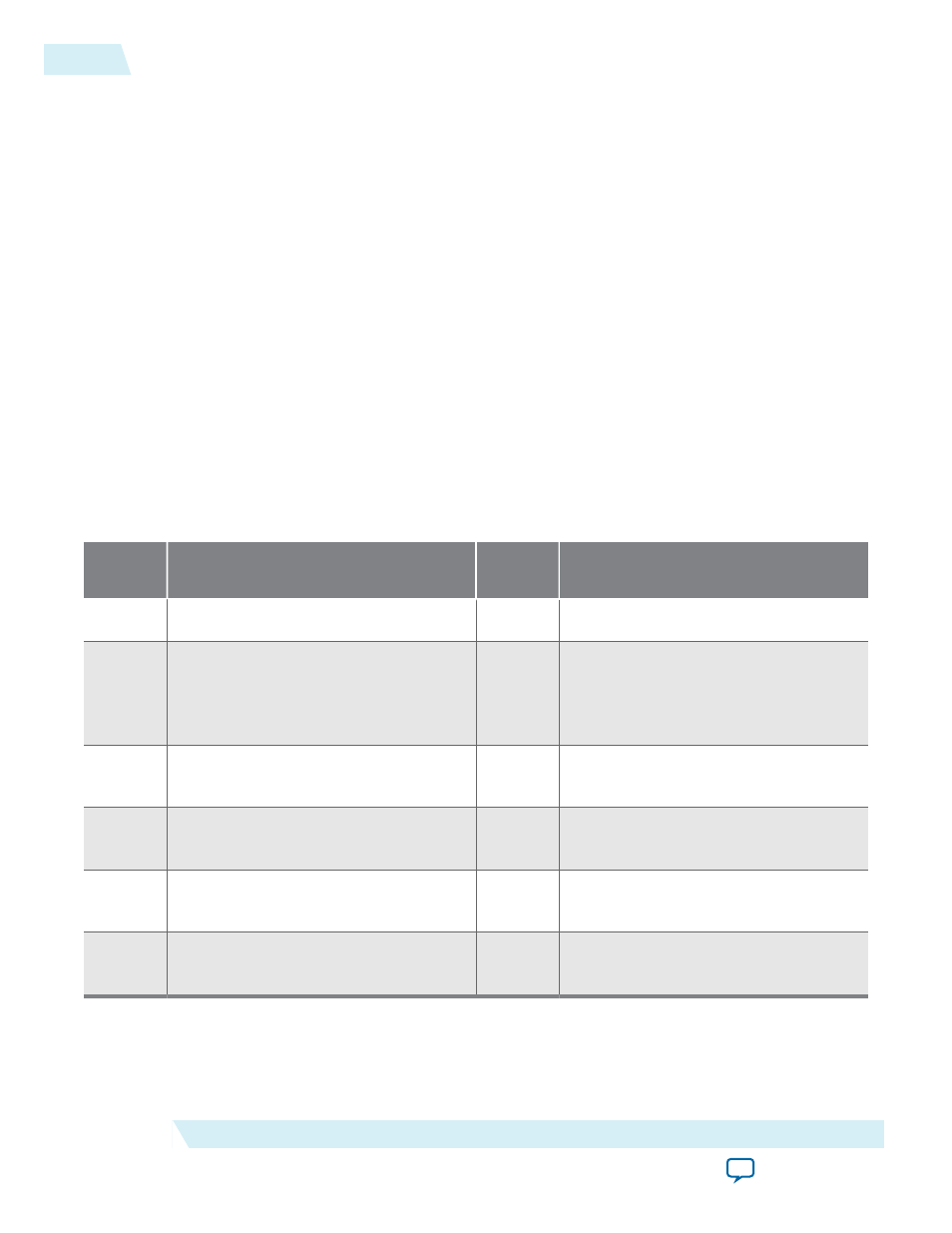

Table 6-24: Avalon‑MM Interrupt Status Registers for Root Ports, 0x3060

Bits

Name

Access

Mode

Description

[31:5] Reserved

—

—

[4]

RPRX_CPL_RECEIVED

RW1C

Set to 1’b1 when the Root Port has

received a Completion TLP for an

outstanding Non-Posted request from

the TLP Direct channel.

[3]

INTD_RECEIVED

RW1C

The Root Port has received INTD from

the Endpoint.

[2]

INTC_RECEIVED

RW1C

The Root Port has received INTC from

the Endpoint.

[1]

INTB_RECEIVED

RW1C

The Root Port has received INTB from

the Endpoint.

[0]

INTA_RECEIVED

RW1C

The Root Port has received INTA from

the Endpoint.

6-28

Sending a Read TLP or Receiving a Non-Posted Completion TLP

UG-01145_avmm

2015.05.14

Altera Corporation

Registers