Generating the example design, Generating the example design -3 – Altera Arria 10 Avalon-MM User Manual

Page 21

Generating the Example Design

1. On the Generate menu, select Generate Testbench System. The Generation dialog box appears.

2. Under Testbench System, set the following options:

a. For Create testbench Qsys system, select Standard, BFMs for standard Qsys interfaces.

b. For Create testbench simulation model, select Verilog.

3. You can retain the default values for all other parameters.

4. Click Generate.

5. After Qsys reports Generation Completed, click Close.

6. On the File menu, click Save.

The following table lists the testbench and simulation directories Qsys generates.

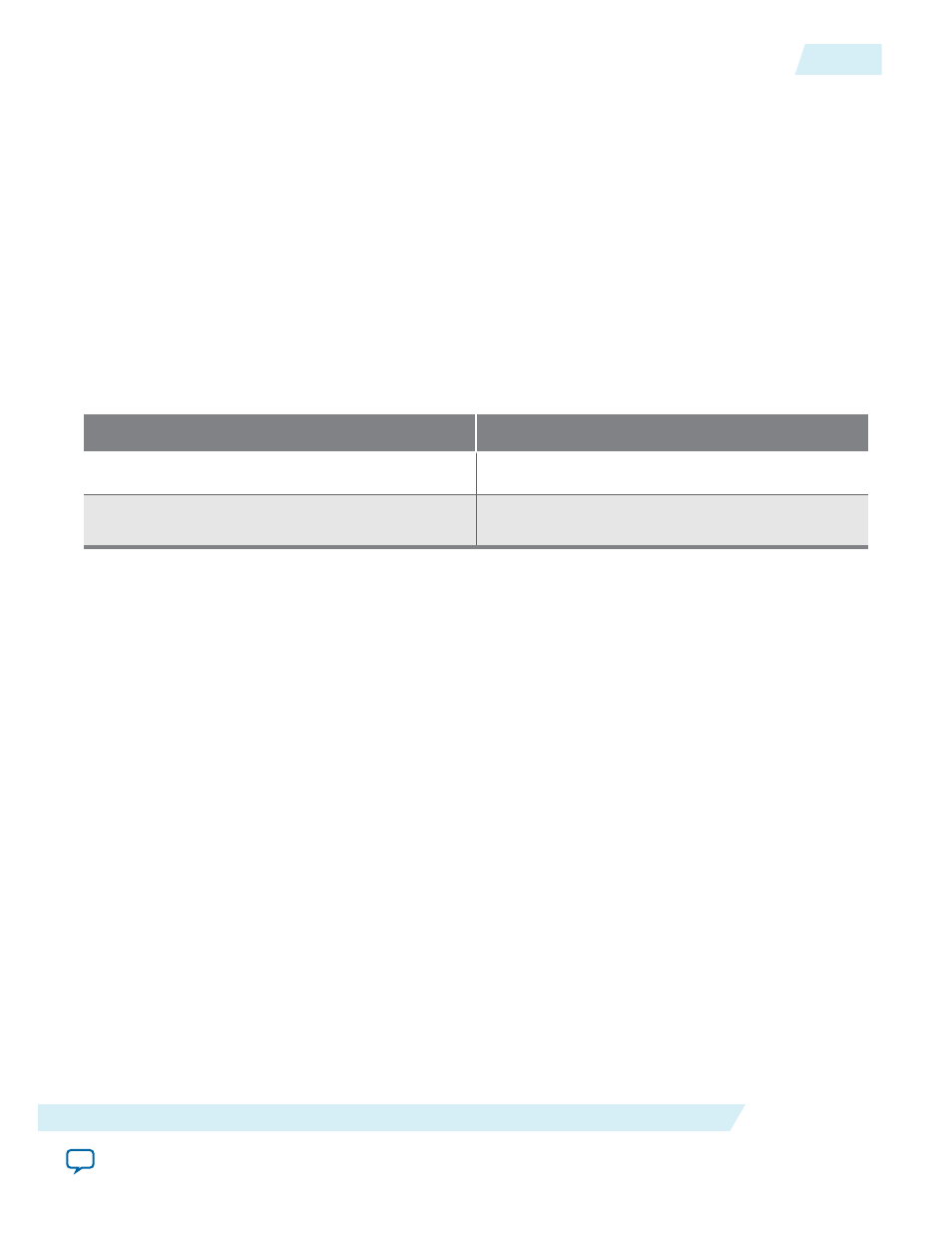

Table 2-1: Qsys System Generated Directories

Directory

Location

Qsys system

<project_dir>/ep_g2x4_avmm128_tb

Simulation Directory

<project_dir>/ep_g2x4_avmm128_tb/ep_g2x4_tb/sim/

<cad_vendor>

The design example simulation includes the following components and software:

• The Qsys system

• A testbench. You can view this testbench in Qsys by opening

<project_dir>/ep_g2x4_avmm128_tb/ep_

g2x4_avmm128_tb.qsys

.

• The ModelSim software

Note: You can also use any other supported third-party simulator to simulate your design.

Complete the following steps to run the Qsys testbench:

1. In a terminal window, change to the

<project_dir>/ep_g2x4_avmm128_tb/ep_g2x4_avmm128_tb/sim/

mentor

directory.

2. Start the ModelSim

®

simulator.

3. Type the following commands in a terminal window:

a.

do msim_setup.tcl

b.

ld_debug

c.

run 140000 ns

UG-01145_avmm

2015.05.14

Generating the Example Design

2-3

Getting Started with the Avalon‑MM Arria 10 Hard IP for PCI Express

Altera Corporation