Setting up simulation, Changing between serial and pipe simulation, Viewing the important pipe interface signals – Altera Arria 10 Avalon-MM User Manual

Page 199: Setting up simulation -49, Changing between serial and pipe simulation -49, Viewing the important pipe interface signals -49

Related Information

BFM Log and Message Procedures

on page 14-34

Setting Up Simulation

Changing the simulation parameters reduces simulation time and provides greater visibility.

Changing Between Serial and PIPE Simulation

By default, the Altera testbench runs a serial simulation. You can change between serial and PIPE

simulation by editing the top-level testbench file.

The

serial_sim_hwtcl

and

enable_pipe32_phyip_ser_driver_hwtcl

parameters control whether

simulation is in serial mode or PIPE simulation mode. The parameters are defined in the top-level

testbench,

<working_dir>/ep_g1x8_tb/ep_g1x8_tb/sim/ep_g1x8_tb.v

.

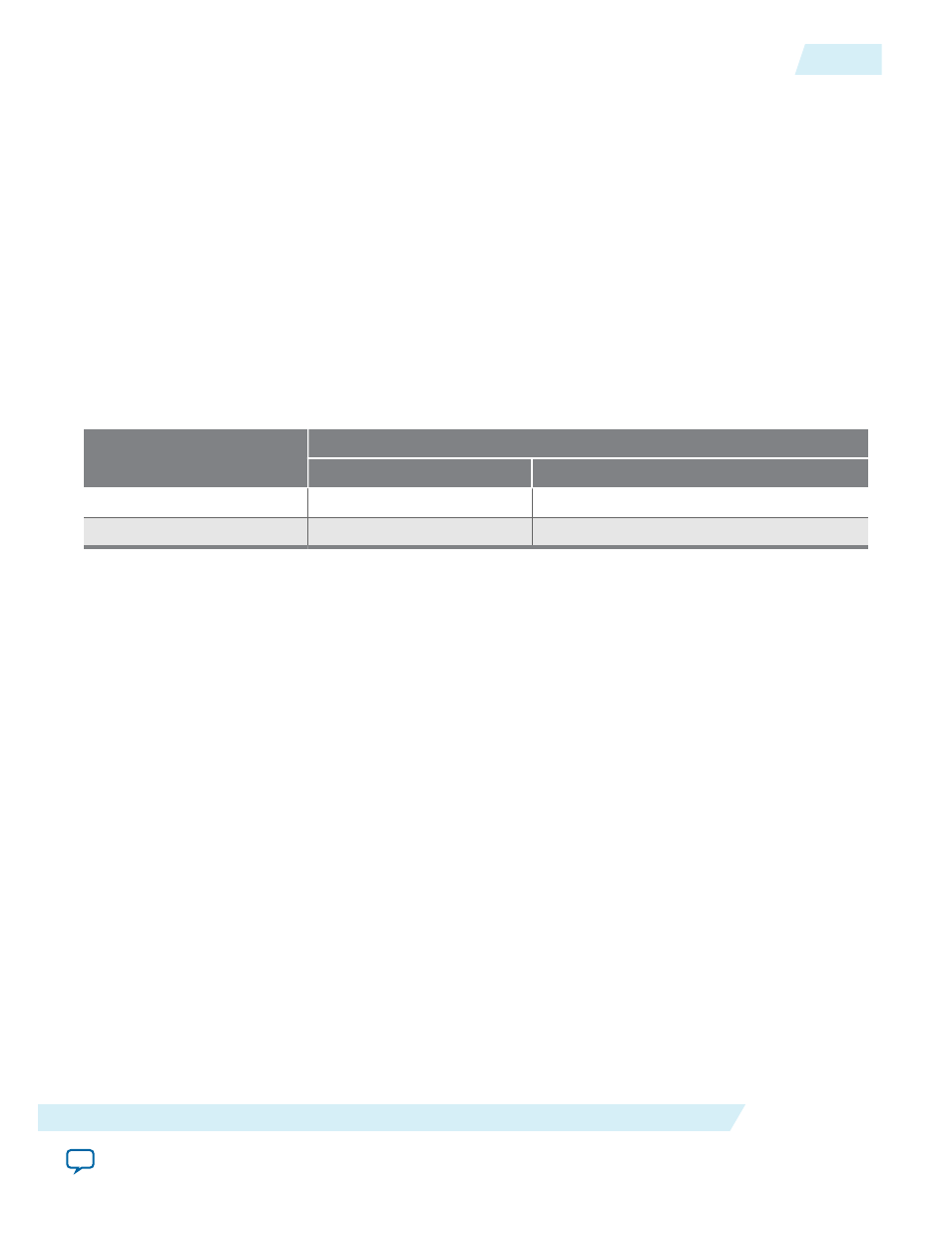

Table 14-13: Controlling Serial and PIPE Simulations

Data Rates

Parameter Settings

serial_sim_hwtcl

enable_pipe32_phyip_ser_driver_hwtcl

Serial simulation

1

0

PIPE simulation

0

1

Using the PIPE Interface for Gen1 and Gen2 Variants

Running the simulation in PIPE mode reduces simulation time and provides greater visibility.

Complete the following steps to simulate using the PIPE interface:

1. Change to your simulation directory,

<work_dir>/<variant>/testbench/<variant>_tb/simulation

2. Open

<variant>_tb.v

.

3. Search for the string,

serial_sim_hwtcl

. Set the value of this parameter to 0 if it is 1.

4. Save

<variant>_tb.v

.

Viewing the Important PIPE Interface Signals

You can view the most important PIPE interface signals,

txdata

,

txdatak

,

rxdata

, and

rxdatak

at the

following level of the design hierarchy:

altpcie_<device>_hip_pipen1b|

twentynm_hssi_<gen>_<lanes>_pcie_hip

.

Disabling the Scrambler for Gen1 and Gen2 Simulations

The encoding scheme implemented by the scrambler applies a binary polynomial to the data stream to

ensure enough data transitions between 0 and 1 to prevent clock drift. The data is decoded at the other

end of the link by running the inverse polynomial.

UG-01145_avmm

2015.05.14

Setting Up Simulation

14-49

Avalon-MM Testbench and Design Example

Altera Corporation