Example designs, Example designs -9 – Altera Arria 10 Avalon-MM User Manual

Page 15

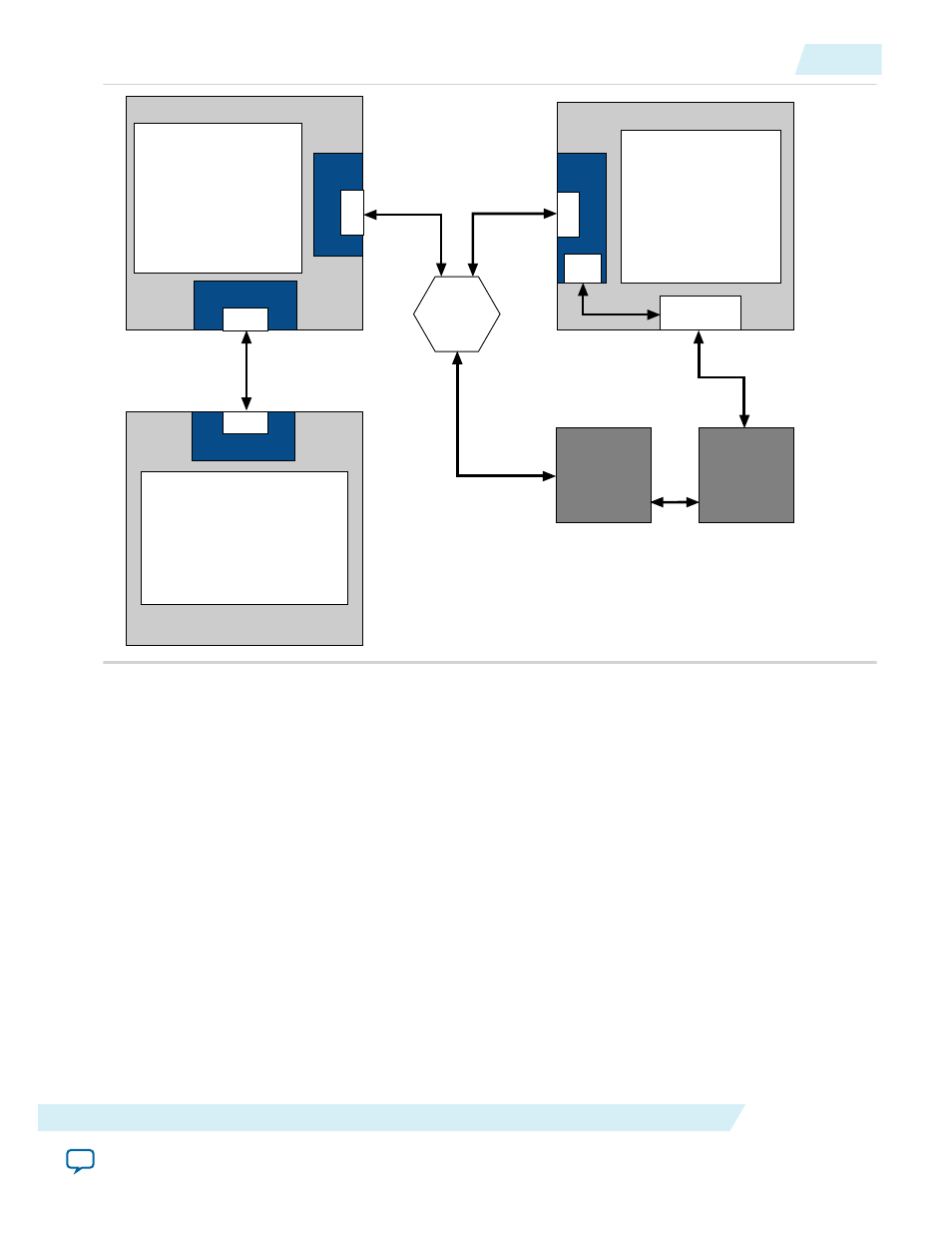

PCIe Link

PCIe Hard IP

RP

Switch

PCIe

Hard IP

RP

User Application

Logic

PCIe Hard IP

EP

PCIe Link

PCIe Link

User Application

Logic

Altera FPGA Hard IP for PCI Express

Altera FPGA with Hard IP for PCI Express

Active Serial or

Active Quad

Device Configuration

Configuration via Protocol (CvP)

using the PCI Express Link

Serial or

Quad Flash

USB

Download

cable

PCIe

Hard IP

EP

User

Application

Logic

Altera FPGA with Hard IP for PCI Express

Config

Control

CVP

USB

Host CPU

PCIe

Related Information

Example Designs

Qsys example designs are available for the Avalon-MM Arria 10 Hard IP for PCI Express IP Core. You

can download them from the

<install_dir>/ip/altera/altera_pcie/altera_pcie_a10_ed/example_design/a10

directory:

When you click the Example Design button in the Parameter Editor, you are prompted to specify the

example design location. After example design generation completes, this directory contains one or two

example designs. One is the example design from the

<install_dir>

that best matches the current parameter

settings. This example design provides a static DUT. The other example design is a customized example

design that matches your parameter settings exactly; starting in the Quartus II software v15.0, this feature

is available for most but not all IP core variations. If this feature is not available for your particular

parameter settings, the Parameter Editor displays a warning.

Related Information

Getting Started with the Avalon-MM Arria 10 Hard IP for PCI Express

on page 2-1

UG-01145_avmm

2015.05.14

Example Designs

1-9

Datasheet

Altera Corporation