Altera Arria 10 Avalon-MM User Manual

Page 85

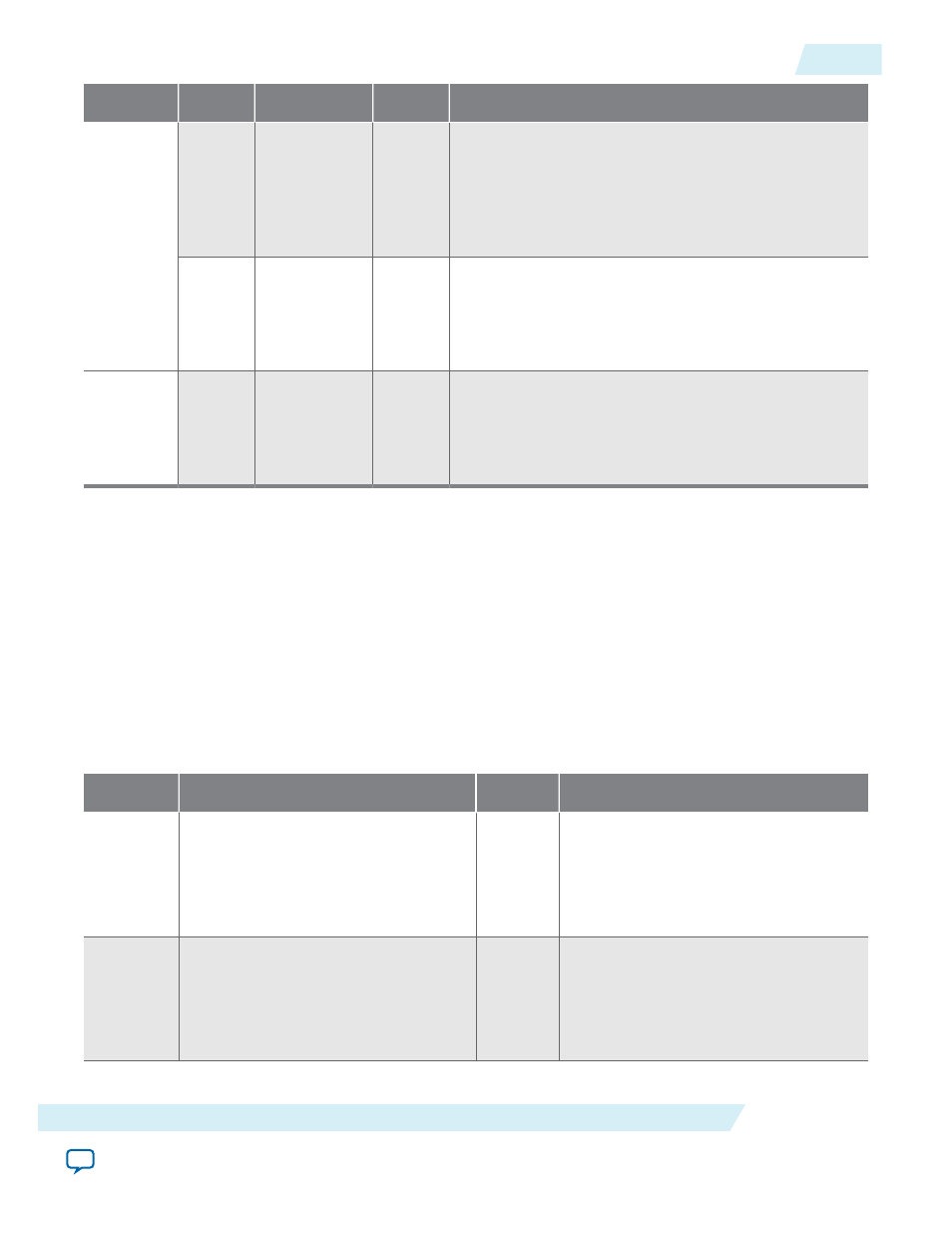

Address

Bits

Name

Access

Description

0x1008

[1:0]

A2P_ADDR_

SPACE1

RW

Address space indication for entry 1. This entry is

available only if the number of translation table entries

(Number of address pages) is greater than 1.

The same encodings are defined for A2P_ADDR_

SPACE1 as for A2P_ADDR_SPACE0.:

[31:2]

A2P_ADDR_

MAP_LO1

RW

Lower bits of Avalon-MM-to-PCI Express address map

entry 1.

This entry is only implemented if the number of

address translation table entries is greater than 1.

0x100C [31:0]

A2P_ADDR_

MAP_HI1

RW

Upper bits of Avalon-MM-to-PCI Express address map

entry 1.

This entry is only implemented if the number of

address translation table entries is greater than 1.

PCI Express to Avalon-MM Interrupt Status and Enable Registers for Endpoints

The registers in this section contain status of various signals in the PCI Express Avalon-MM bridge logic

and allow Avalon interrupts to be asserted when enabled. A processor local to the interconnect fabric that

processes the Avalon-MM interrupts can access these registers.

Note: These registers must not be accessed by the PCI Express Avalon-MM bridge master ports; however,

there is nothing in the hardware that prevents a PCI Express Avalon-MM bridge master port from

accessing these registers.

The following table describes the Interrupt Status register when you configure the core as an Endpoint. It

records the status of all conditions that can cause an Avalon-MM interrupt to be asserted.

Table 6-19: PCI Express to Avalon-MM Interrupt Status Register for Endpoints, 0x3060

Bits

Name

Access

Description

0

ERR_PCI_WRITE_FAILURE

RW1C

When set to 1, indicates a PCI Express

write failure. This bit can also be cleared

by writing a 1 to the same bit in the

Avalon

MM to PCI Express

Interrupt Status

register.

1

ERR_PCI_READ_FAILURE

RW1C

When set to 1, indicates the failure of a

PCI Express read. This bit can also be

cleared by writing a 1 to the same bit in

the

Avalon

MM to PCI Express

Interrupt Status

register.

UG-01145_avmm

2015.05.14

PCI Express to Avalon-MM Interrupt Status and Enable Registers for...

6-19

Registers

Altera Corporation