Altera Arria 10 Avalon-MM User Manual

Page 43

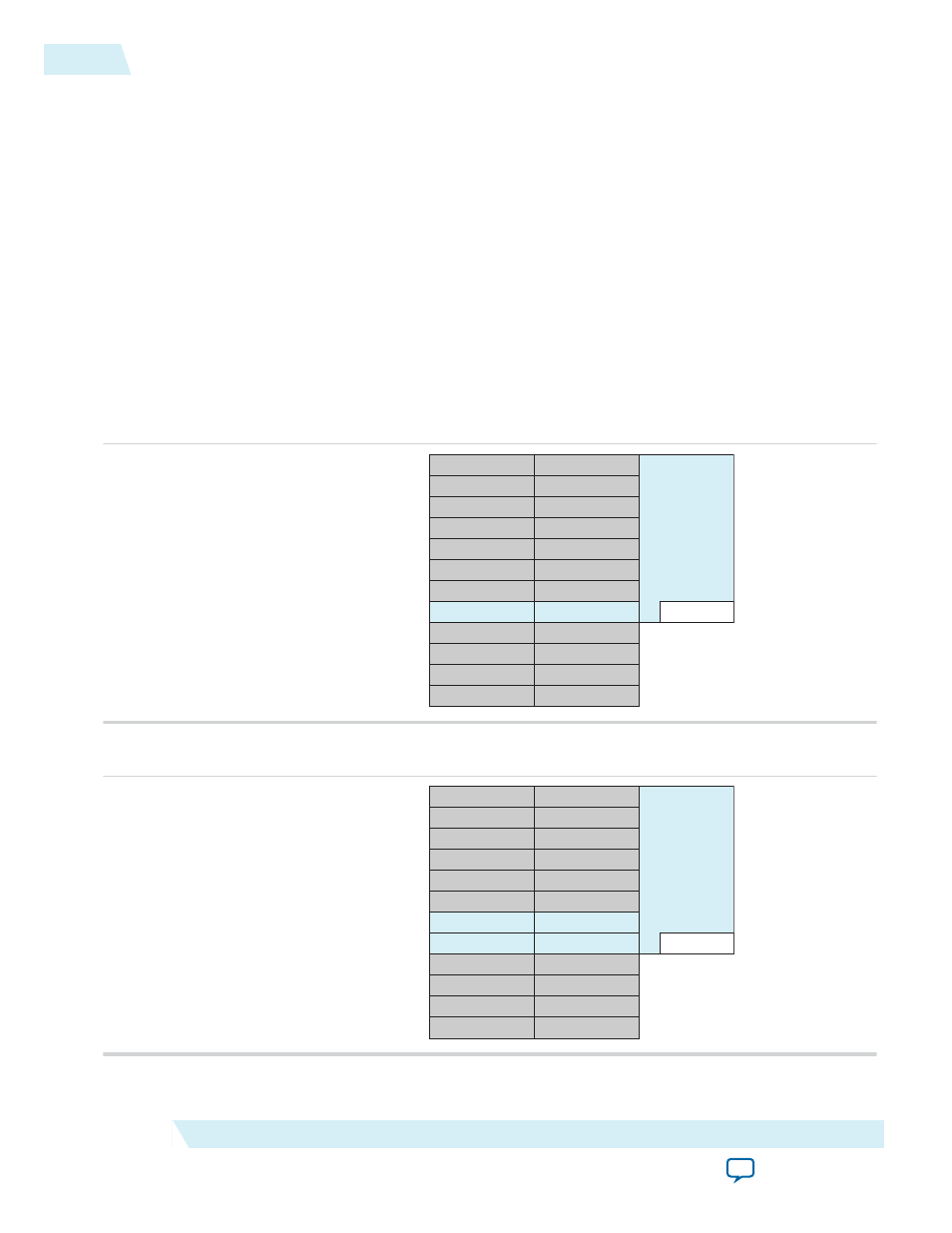

Channel and Pin Placement for the Gen1, Gen2, and Gen3 Data Rates

The following figures illustrate the x1, x2, x4, and x8 channel and pin placements for the Arria 10 Hard IP

for PCI Express.

In these figures, channels that are not used for the PCI Express protocol are available for other protocols.

Unused channels are shown in gray.

Note: In all configurations, physical channel 4 in the PCS connects to logical channel 0 in the hard IP.

You cannot change the channel placements illustrated below.

For the possible values of <txvr_block_N> and <txvr_block_N+1>, refer to the figures that show the

physical location of the Hard IP PCIe blocks in the different types of Arria 10 devices, at the start of this

chapter. For each HIP block, the transceiver block that is adjacent and extends below the HIP block, is

<txvr_block_N>, and the transceiver block that is directly above <txvr_block_N> is <txvr_block_N+1>.

For example, in an Arria 10 device with 96 transceiver channels and four PCIe HIP blocks, if your design

uses the HIP block that supports CvP, <txvr_block_N> is GXB1C and <txvr_block_N+1> is GXB1D.

Figure 4-4: Arria 10 Gen1, Gen2, and Gen3 x1 Channel and Pin Placement

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 2

PMA Channel 0

PMA Channel 3

PMA Channel 2

PMA Channel 1

PMA Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 2

PCS Channel 0

PCS Channel 3

PCS Channel 2

PCS Channel 1

PCS Channel 0

Hard IP Ch0

PMA Channel 1

PCS Channel 1

PMA Channel 4

PCS Channel 4

PMA Channel 5

PCS Channel 5

Hard IP

for PCIe

<txvr_block_N>_TX/RX_CH4N

Figure 4-5: Arria 10 Gen1 Gen2, and Gen3 x2 Channel and Pin Placement

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 2

PMA Channel 0

PMA Channel 3

PMA Channel 2

PMA Channel 1

PMA Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 2

PCS Channel 0

PCS Channel 3

PCS Channel 2

PCS Channel 1

PCS Channel 0

Hard IP Ch0

PMA Channel 1

PCS Channel 1

PMA Channel 4

PCS Channel 4

PMA Channel 5

PCS Channel 5

Hard IP

for PCIe

<txvr_block_N>_TX/RX_CH4N

<txvr_block_N>_TX/RX_CH5N

4-4

Channel and Pin Placement for the Gen1, Gen2, and Gen3 Data Rates

UG-01145_avmm

2015.05.14

Altera Corporation

Physical Layout of Hard IP In Arria 10 Devices