Altera Arria 10 Avalon-MM User Manual

Page 91

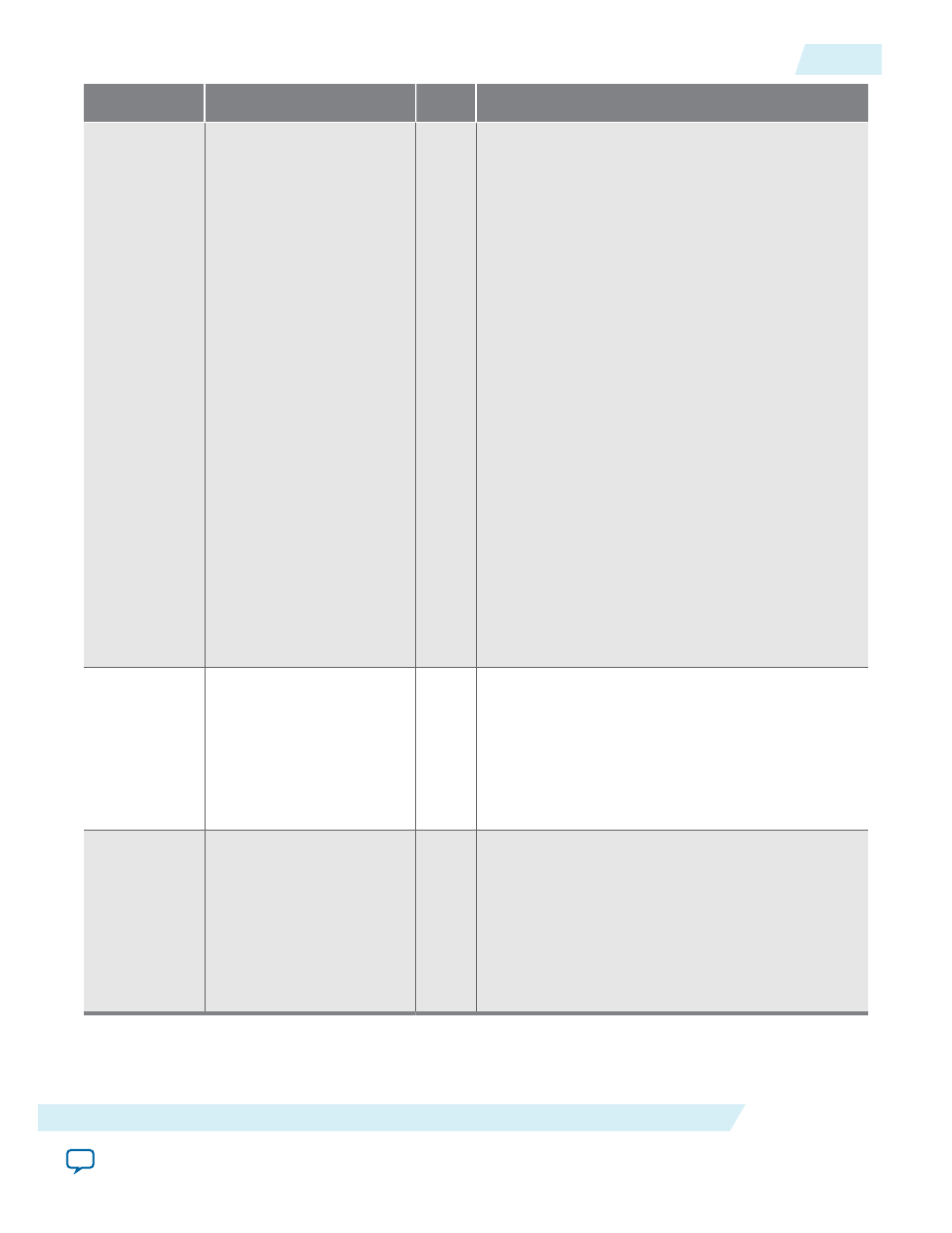

Byte Offset

Register

Dir

Description

• 00101: Polling.Speed

• 00110: config.Linkwidthstart

• 00111: Config.Linkaccept

• 01000: Config.Lanenumaccept

• 01001: Config.Lanenumwait

• 01010: Config.Complete

• 01011: Config.Idle

• 01100: Recovery.Rcvlock

• 01101: Recovery.Rcvconfig

• 01110: Recovery.Idle

• 01111: L0

• 10000: Disable

• 10001: Loopback.Entry

• 10010: Loopback.Active

• 10011: Loopback.Exit

• 10100: Hot.Reset

• 10101: LOs

• 11001: L2.transmit.Wake

• 11010: Speed.Recovery

• 11011: Recovery.Equalization, Phase 0

• 11100: Recovery.Equalization, Phase 1

• 11101: Recovery.Equalization, Phase 2

• 11110: recovery.Equalization, Phase 3

14'h3C68

current_speed_reg[1:0]

O

Indicates the current speed of the PCIe link. The

following encodings are defined:

• 2b’00: Undefined

• 2b’01: Gen1

• 2b’10: Gen2

• 2b’11: Gen3

14'h3C6C

lane_act_reg[3:0]

O

Lane Active Mode: This signal indicates the number

of lanes that configured during link training. The

following encodings are defined:

• 4’b0001: 1 lane

• 4’b0010: 2 lanes

• 4’b0100: 4 lanes

• 4’b1000: 8 lanes

UG-01145_avmm

2015.05.14

Control Register Access (CRA) Avalon-MM Slave Port

6-25

Registers

Altera Corporation