Altera Arria 10 Avalon-MM User Manual

Page 90

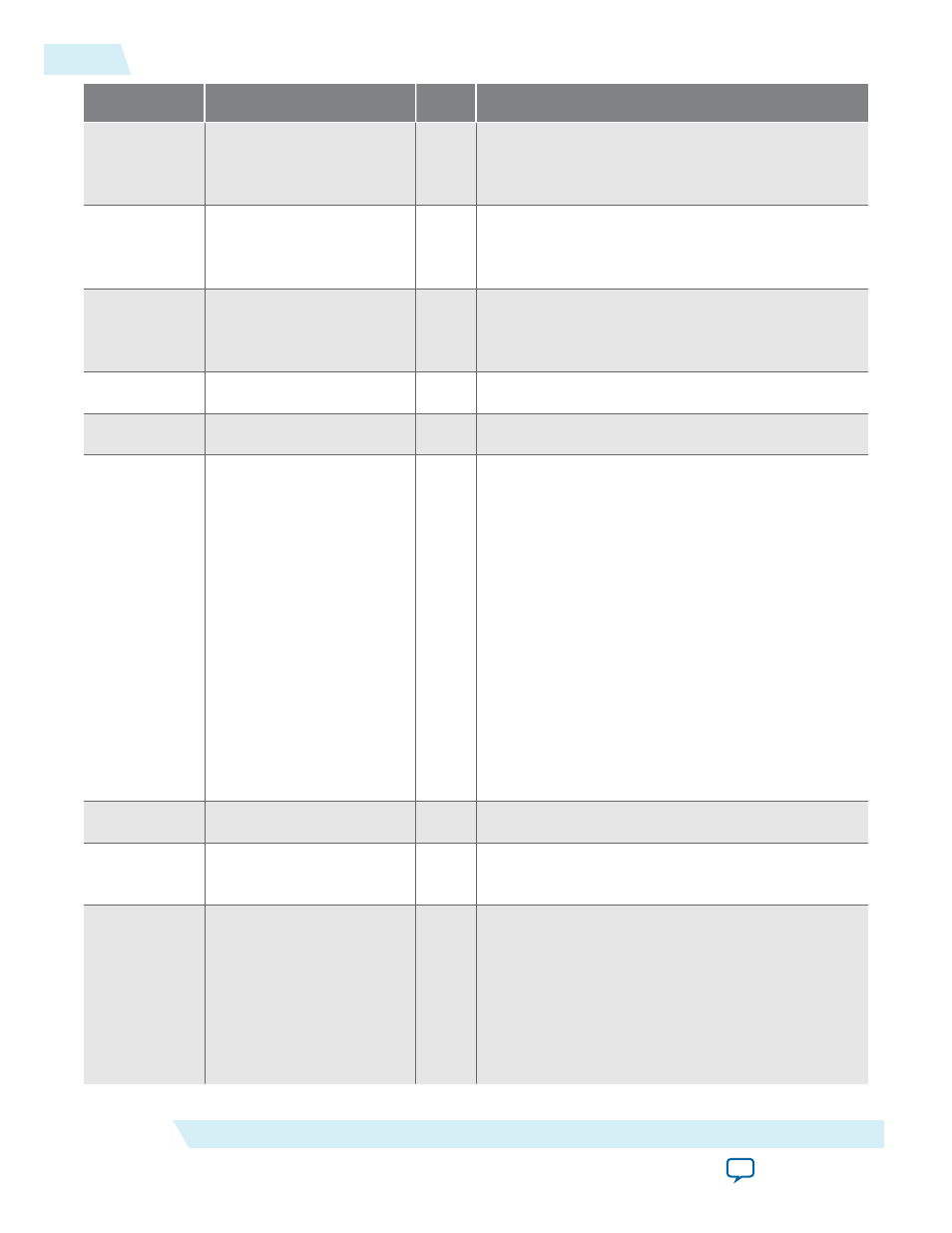

Byte Offset

Register

Dir

Description

14'h3C44

cfg_pr_lim_low[31:0]

O

The lower 32 bits of the prefetchable limit registers

of the Type1 Configuration Space. Available in Root

Port mode.

14'h3C48

cfg_pr_lim_hi[43:32]

O

The upper 12 bits of the prefetchable limit registers

of the Type1 Configuration Space. Available in Root

Port mode.

14'h3C4C

cfg_pmcsr[31:0]

O

cfg_pmcsr[31:16]

is Power Management Control

and

cfg_pmcsr[15:0]

is the Power Management

Status register.

14'h3C50

cfg_msixcsr[15:0]

O

MSI-X message control register.

14'h3C54

cfg_msicsr[15:0]

O

MSI message control.

14'h3C58

cfg_tcvcmap[23:0]

O

Configuration traffic class (TC)/virtual channel

(VC) mapping. The Application Layer uses this

signal to generate a TLP mapped to the appropriate

channel based on the traffic class of the packet.

The following encodings are defined:

•

cfg_tcvcmap[2:0]

: Mapping for TC0 (always 0)

.

•

cfg_tcvcmap[5:3]

: Mapping for TC1.

•

cfg_tcvcmap[8:6]

: Mapping for TC2.

•

cfg_tcvcmap[11:9]

: Mapping for TC3.

•

cfg_tcvcmap[14:12]

: Mapping for TC4.

•

cfg_tcvcmap[17:15]

: Mapping for TC5.

•

cfg_tcvcmap[20:18]

: Mapping for TC6.

•

cfg_tcvcmap[23:21]

: Mapping for TC7.

14'h3C5C

cfg_msi_data[15:0]

O

cfg_msi_data[15:0]

is message data for MSI.

14'h3C60

cfg_busdev[12:0]

O

Bus/Device Number captured by or programmed in

the Hard IP.

14'h3C64

ltssm_reg[4:0]

O

Specifies the current LTSSM state. The LTSSM state

machine encoding defines the following states:

• 00000: Detect.Quiet

• 00001: Detect.Active

• 00010: Polling.Active

• 00011: Polling.Compliance

• 00100: Polling.Configuration

6-24

Control Register Access (CRA) Avalon-MM Slave Port

UG-01145_avmm

2015.05.14

Altera Corporation

Registers