Altera Arria 10 Avalon-MM User Manual

Page 31

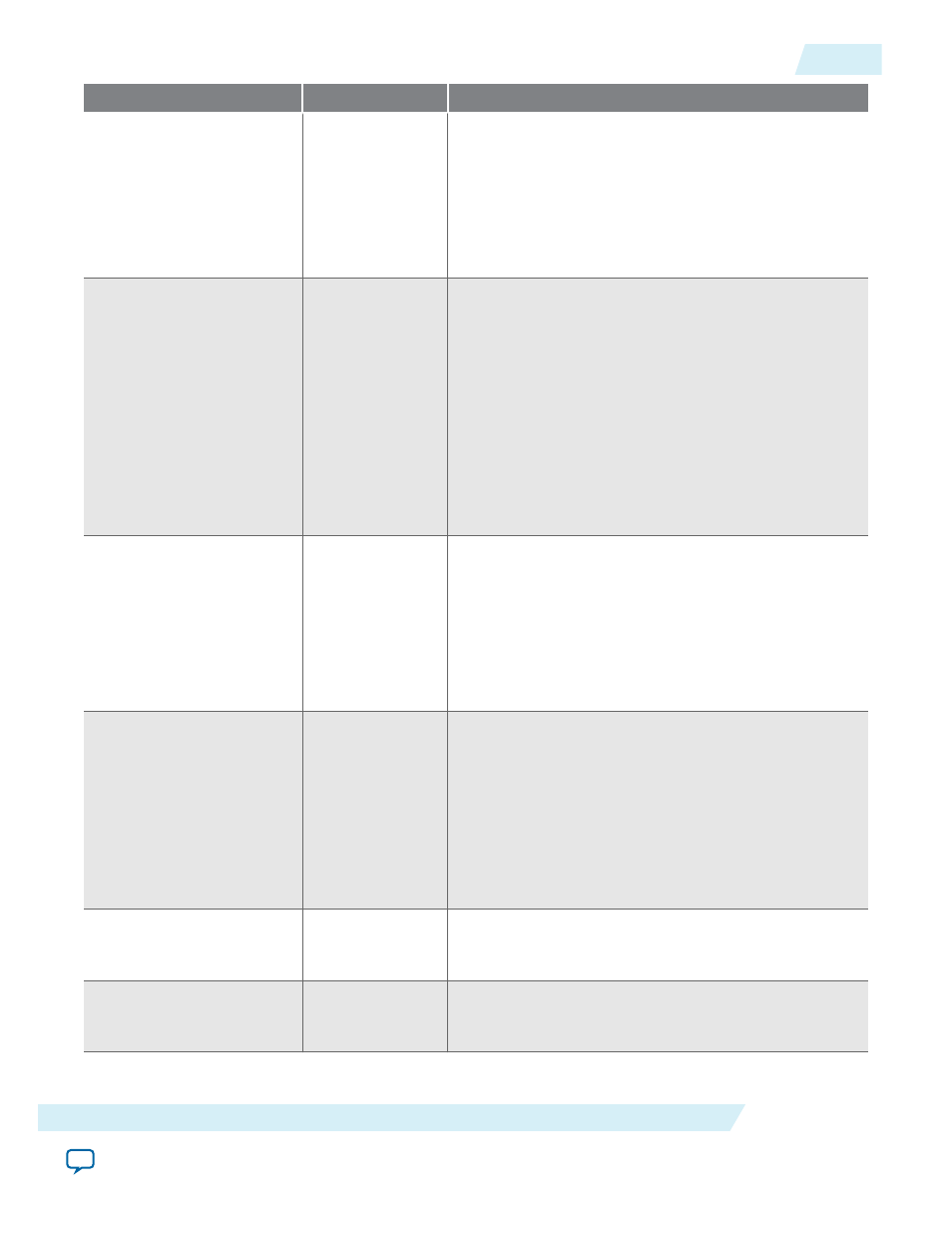

Parameter

Value

Description

Enable control register

access (CRA) Avalon-MM

slave port

On/Off

Allows read and write access to bridge registers from the

interconnect fabric using a specialized slave port. This

option is required for Requester/Completer variants

and optional for Completer Only variants. Enabling

this option allows read and write access to bridge

registers, except in the Completer-Only single dword

variations.

Export MSI/MSI-X

conduit interfaces

On/Off

When you turn this option on, the core exports

top-level MSI and MSI-X interfaces that you can use to

implement a Custom Interrupt Handler for MSI and

MSI-X interrupts. For more information about the

Custom Interrupt Handler, refer to Interrupts for End

Points Using the Avalon-MM Interface with Multiple

MSI/MSI

-

X Support. If you turn this option Off, the

core handles interrupts internally.

If you select this option, you must design your own

external descriptor controller. The embedded controller

does not support MSI-X.

Enable PCIe interrupt at

power-on

On/Off

When you turn this option on, the Avalon-MM Arria 10

Hard IP for PCI Express enables the interrupt register at

power-up. Turning off this option disables the interrupt

register at power-up. The setting does not affect run-

time configuration of the interrupt enable register.

For the Avalon-MM interface with DMA, this value

must be off.

Enable Hard IP Status

Bus when using the

AVMM interface

On/Off

When you turn this option on, your top-level variant

includes the following top-level signals:

• Link status signals

• ECC error signals

• TX and RX parity error signals

• Completion header and data signals, indicating the

total number of Completion TLPs currently stored in

the RX buffer.

Address width of

accessible PCIe memory

space

20–64

Specifies the size of the PCIe memory space. The value

you specify sets the width of the TX slave address,

txs_

address

for 64-bit addresses.

Number of address pages 2, 4, 8, 16, 32, 64,

128, 256, 512

Specifies the number of consecutive address pages in the

PCI Express address domain. This parameter is only

necessary for 32-bit addresses.

UG-01145_avmm

2015.05.14

Interface System Settings

3-5

Parameter Settings

Altera Corporation