Physical layer interface signals, Serial data signals, Physical layer interface signals -13 – Altera Arria 10 Avalon-MM User Manual

Page 60: Serial data signals -13

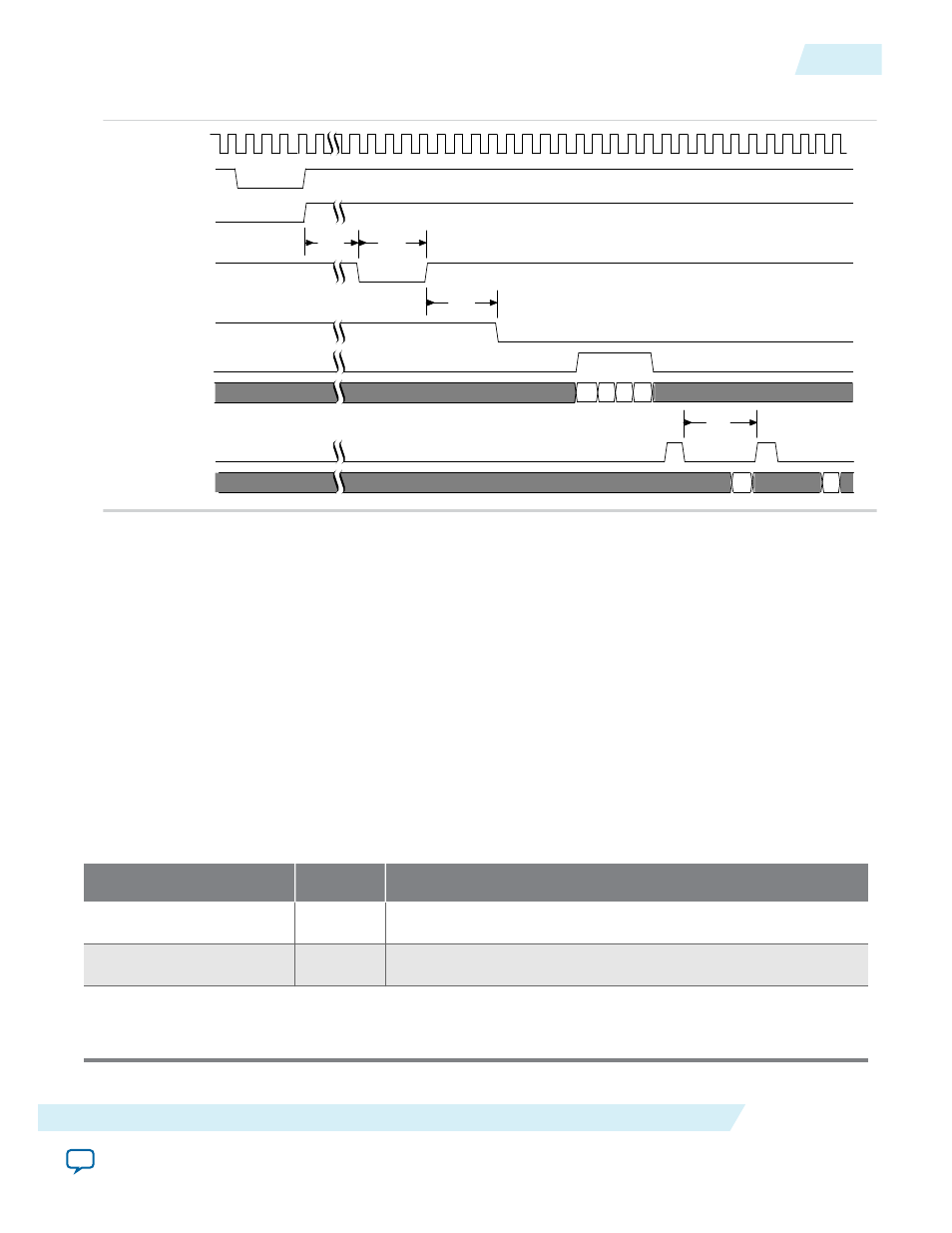

Figure 5-6: Hard IP Reconfiguration Bus Timing of Read-Only Registers

avmm_clk

hip_reconfig_rst_n

user_mode

ser_shift_load

interface_sel

avmm_wr

avmm_wrdata[15:0]

avmm_rd

avmm_rdata[15:0]

D0

D0

D1

D1

D2 D3

324 ns

4 clks

4 clks

4 clks

For a detailed description of the Avalon-MM protocol, refer to the Avalon Memory Mapped Interfaces

chapter in the Avalon Interface Specifications.

Related Information

Physical Layer Interface Signals

Altera provides an integrated solution with the Transaction, Data Link and Physical Layers. The IP

Parameter Editor generates a SERDES variation file,

<variation>_serdes.v

or .vhd , in addition to the Hard

IP variation file,

<variation>.v

or

.vhd

. The SERDES entity is included in the library files for PCI Express.

Serial Data Signals

Table 5-8: 1-Bit Interface Signals

Signal

Direction

Description

tx_out[7:0]

(1)

Output

Transmit output. These signals are the serial outputs of lanes 7–0.

rx_in[7:0]

(1)

Input

Receive input. These signals are the serial inputs of lanes 7–0.

Note:

1. The x1 IP core only has lane 0. The x2 IP core only has lanes 1–0. The x4 IP core only has lanes 3–0.

UG-01145_avmm

2015.05.14

Physical Layer Interface Signals

5-13

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation