Altera Arria 10 Avalon-MM User Manual

Page 47

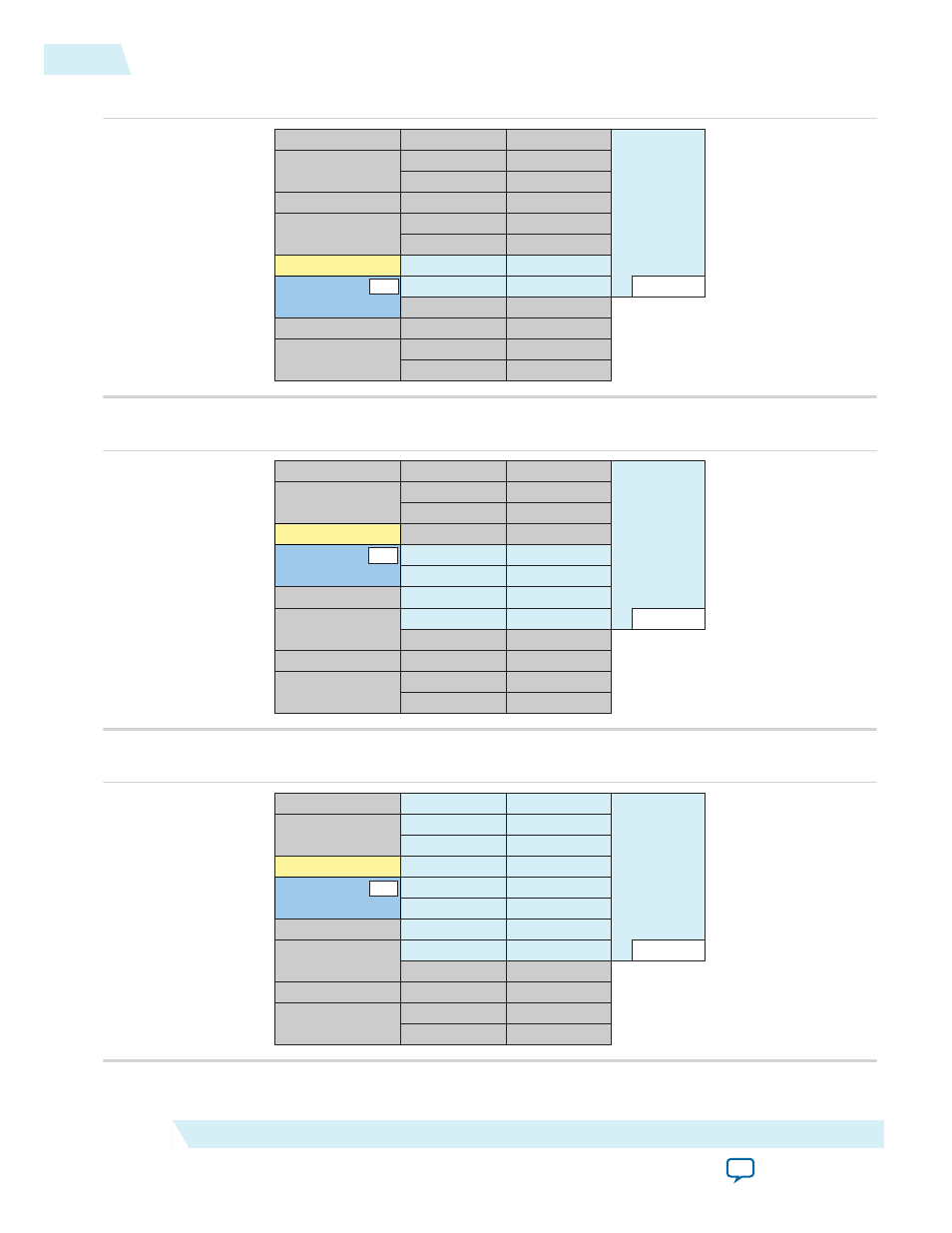

Figure 4-13: Arria 10 Gen3 x2 Channel Placement

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 0

PMA Channel 4

PMA Channel 3

PMA Channel 2

PMA Channel 1

PMA Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 0

PCS Channel 4

PCS Channel 3

PCS Channel 2

PCS Channel 1

PCS Channel 0

Hard IP

for PCIe

fPLL1

ATX1 PLL

fPLL0

ATX0 PLL

fPLL0

ATX0 PLL

Hard IP Ch0

PMA Channel 1

PCS Channel 1

PMA Channel 2

PCS Channel 2

PMA Channel 5

PCS Channel 5

fPLL1

ATX1 PLL

Master

CGB

Master

CGB

indicates the location of the master clock generation block (CGB)

Figure 4-14: Arria 10 Gen3 x4 Channel Placement

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 0

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 2

PMA Channel 1

PMA Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 2

PCS Channel 1

PCS Channel 0

Hard IP

for PCIe

fPLL1

ATX1 PLL

fPLL0

ATX0 PLL

fPLL1

ATX1 PLL

fPLL0

ATX0 PLL

Hard IP Ch0

PMA Channel 1

PCS Channel 1

PMA Channel 2

PCS Channel 2

Master

CGB

Master

CGB

indicates the location of the master clock generation block (CGB)

Figure 4-15: Gen3 x8 Channel Placement

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 0

PMA Channel 5

PMA Channel 4

PMA Channel 3

PMA Channel 2

PMA Channel 1

PMA Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 0

PCS Channel 5

PCS Channel 4

PCS Channel 3

PCS Channel 2

PCS Channel 1

PCS Channel 0

Hard IP

for PCIe

fPLL1

ATX1 PLL

fPLL1

ATX1 PLL

fPLL0

ATX0 PLL

Hard IP Ch0

PMA Channel 1

PCS Channel 1

PMA Channel 2

PCS Channel 2

fPLL0

ATX0 PLL

Master

CGB

Master

CGB

indicates the location of the master clock generation block (CGB)

4-8

Channel Placement and fPLL and ATX PLL Usage for the Gen3 Data Rate

UG-01145_avmm

2015.05.14

Altera Corporation

Physical Layout of Hard IP In Arria 10 Devices