Altera Arria 10 Avalon-MM User Manual

Page 54

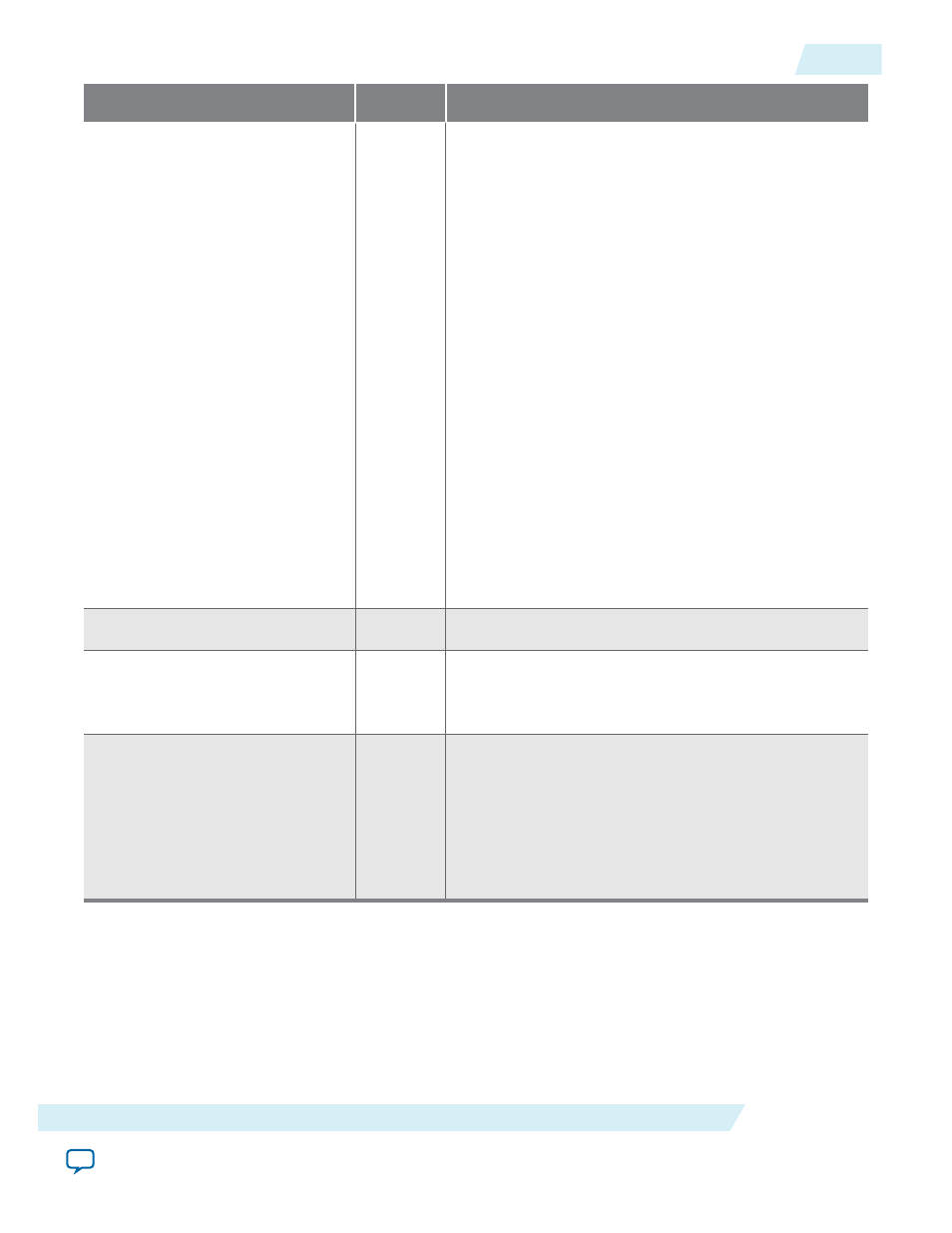

Signal Name

Direction

Description

TxsByteEnable_i[<w>-1:0]

Input

Write byte enable for data. A burst must be continuous.

Therefore all intermediate data phases of a burst must

have a byte enable value of 0xFF. The first and final data

phases of a burst can have other valid values.

For the 128-bit interface, the following restrictions

apply:

• All bytes of a single dword must either be enabled or

disabled

• If more than 1 dword is enabled, the enabled dwords

must be contiguous. The following patterns are legal:

• 16'bF000

• 16'b0F00

• 16'b00F0

• 16'b000F

• 16'bFF00

• 16'b0FF0

• 16'b00FF

• 16'bFFF0

• 16'b0FFF

• 16'bFFFF

TxsReadDataValid_o

Output

Asserted by the bridge to indicate that read data is valid.

TxsReadData_o[127 or 63:0]

Output

The bridge returns the read data on this bus when the

RX read completions for the read have been received

and stored in the internal buffer.

TxsWaitrequest_o

Output

Asserted by the bridge to hold off read or write data

when running out of buffer space. If this signal is

asserted during an operation, the master should

maintain the

TxsRead_i

signal (or

TxsWrite_i

signal

and

TxsWriteData

) stable until after

TxsWaitrequest_

o

is deasserted.

txs_Read

must be deasserted when

TxsWaitrequest_o

is deasserted.

UG-01145_avmm

2015.05.14

64- or 128-Bit Bursting TX Avalon-MM Slave Signals

5-7

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation