Altera Arria 10 Avalon-MM User Manual

Page 77

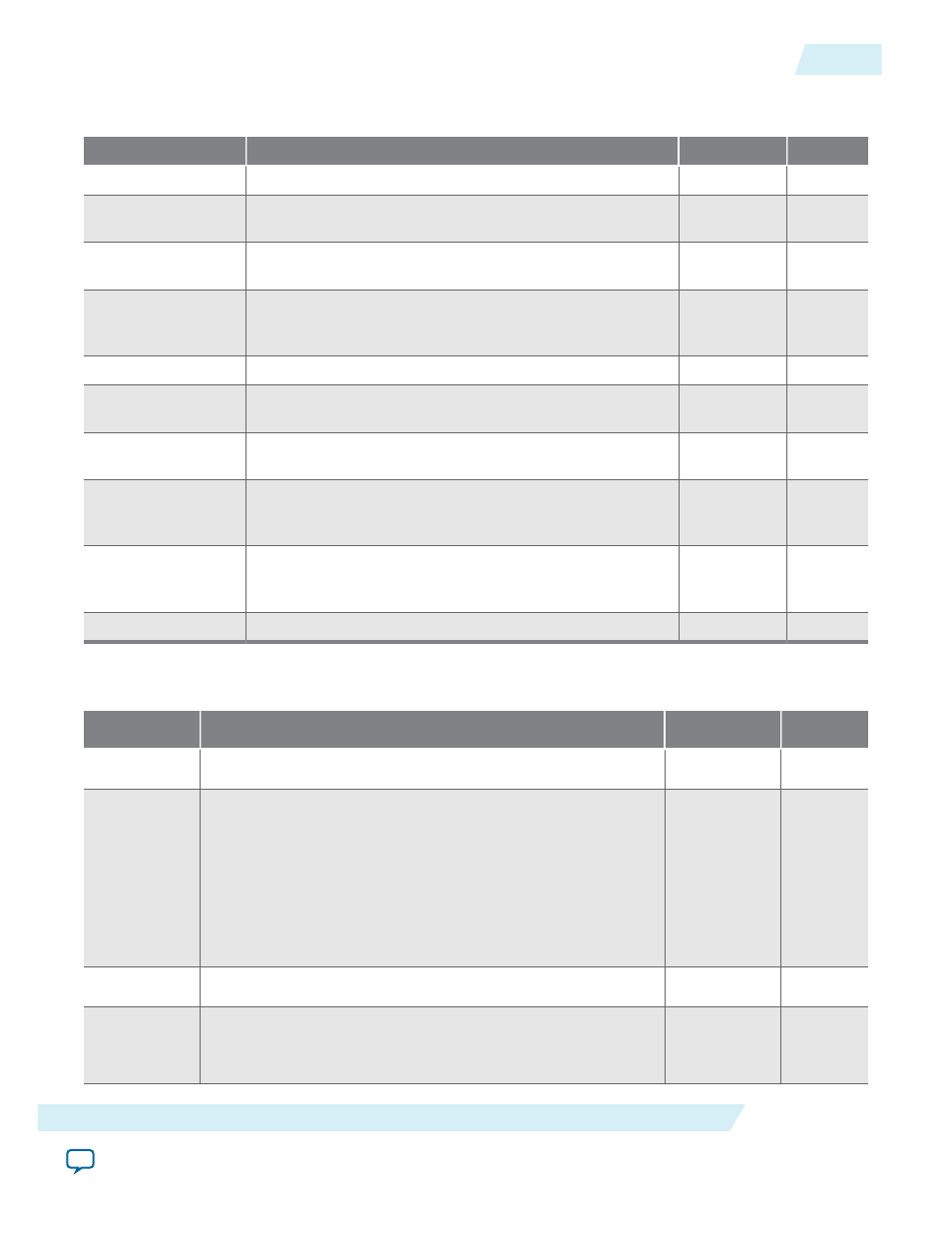

Table 6-7: CvP Status

The

CvP Status

register allows software to monitor the CvP status signals.

Bits

Register Description

Reset Value

Access

[31:26]

Reserved

0x00

RO

[25]

PLD_CORE_READY

. From FPGA fabric. This status bit is

provided for debug.

Variable

RO

[24]

PLD_CLK_IN_USE

. From clock switch module to fabric. This

status bit is provided for debug.

Variable

RO

[23]

CVP_CONFIG_DONE

. Indicates that the FPGA control block has

completed the device configuration via CvP and there were

no errors.

Variable

RO

[22]

Reserved

Variable

RO

[21]

USERMODE

. Indicates if the configurable FPGA fabric is in user

mode.

Variable

RO

[20]

CVP_EN

. Indicates if the FPGA control block has enabled CvP

mode.

Variable

RO

[19]

CVP_CONFIG_ERROR

. Reflects the value of this signal from the

FPGA control block, checked by software to determine if

there was an error during configuration.

Variable

RO

[18]

CVP_CONFIG_READY

. Reflects the value of this signal from the

FPGA control block, checked by software during

programming algorithm.

Variable

RO

[17:0]

Reserved

Variable

RO

Table 6-8: CvP Mode Control

The

CvP Mode Control

register provides global control of the CvP operation.

Bits

Register Description

Reset Value

Access

[31:16]

Reserved.

0x0000

RO

[15:8]

CVP_NUMCLKS

.

This is the number of clocks to send for every CvP data write. Set

this field to one of the values below depending on your configura‐

tion image:

• 0x01 for uncompressed and unencrypted images

• 0x04 for uncompressed and encrypted images

• 0x08 for all compressed images

0x00

RW

[7:3]

Reserved.

0x0

RO

[2]

CVP_FULLCONFIG

. Request that the FPGA control block

reconfigure the entire FPGA including the Arria 10 Hard IP for

PCI Express, bring the PCIe link down.

1’b0

RW

UG-01145_avmm

2015.05.14

CvP Registers

6-11

Registers

Altera Corporation