Programming model for avalon-mm root port, Programming model for avalon-mm root port -26 – Altera Arria 10 Avalon-MM User Manual

Page 92

Programming Model for Avalon-MM Root Port

The Application Layer writes the Root Port TLP TX Data registers with TLP formatted data for Configu‐

ration Read and Write Requests, Message TLPs, Message TLPs with data payload, I/O Read and Write

Requests, or single dword Memory Read and Write Requests. Software should check the Root Port

Link

Status

register (offset 0x92) to ensure the Data Link Layer Link

Active

bit is set to 1'b1 before issuing a

Configuration request to downstream ports.

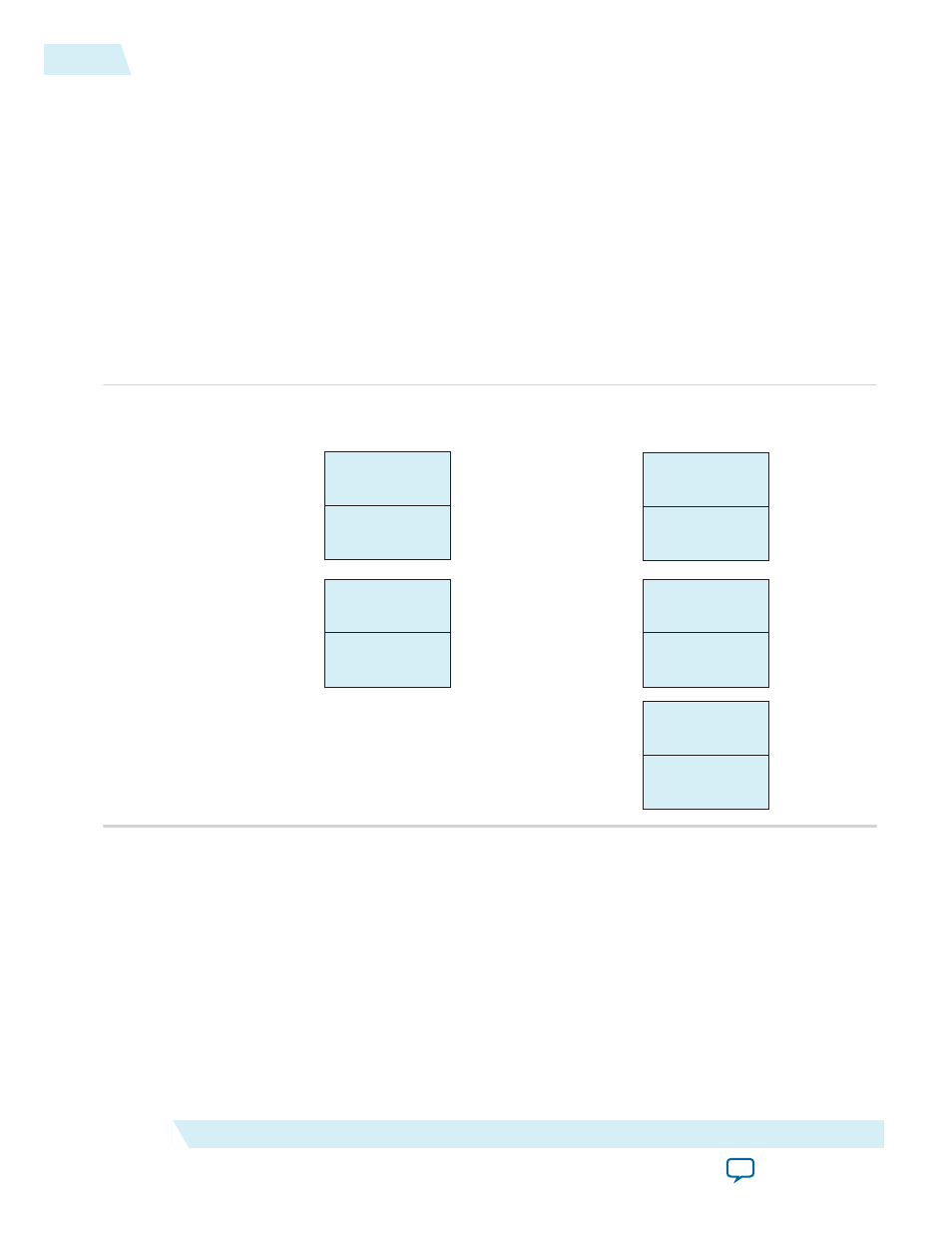

The Application Layer data must be in the appropriate TLP format with the data payload aligned to the

TLP address. Aligning the payload data to the TLP address may result in the payload data being either

aligned or unaligned to the qword. The following figure illustrates three dword TLPs with data that is

aligned and unaligned to the qword.

Figure 6-10: Layout of Data with 3 Dword Headers

Header 1 [63:32]

Cycle 1

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Data Unaligned to

QWord Boundary

Data Aligned to

QWord Boundary

Cycle 2

Header 0 [31:0]

Data [63:32]

Header 2 [31:0]

Header 1 [63:32]

Cycle 1

Header 0 [31:0]

Cycle 2

Header 2 [31:0]

Cycle 3

Data [31:0]

Unused, but must

be written

Unused, but must

be written

The following figure illustrates four dword TLPs with data that are aligned and unaligned to the qword.

6-26

Programming Model for Avalon-MM Root Port

UG-01145_avmm

2015.05.14

Altera Corporation

Registers