Sending a write tlp, Sending a write tlp -27 – Altera Arria 10 Avalon-MM User Manual

Page 93

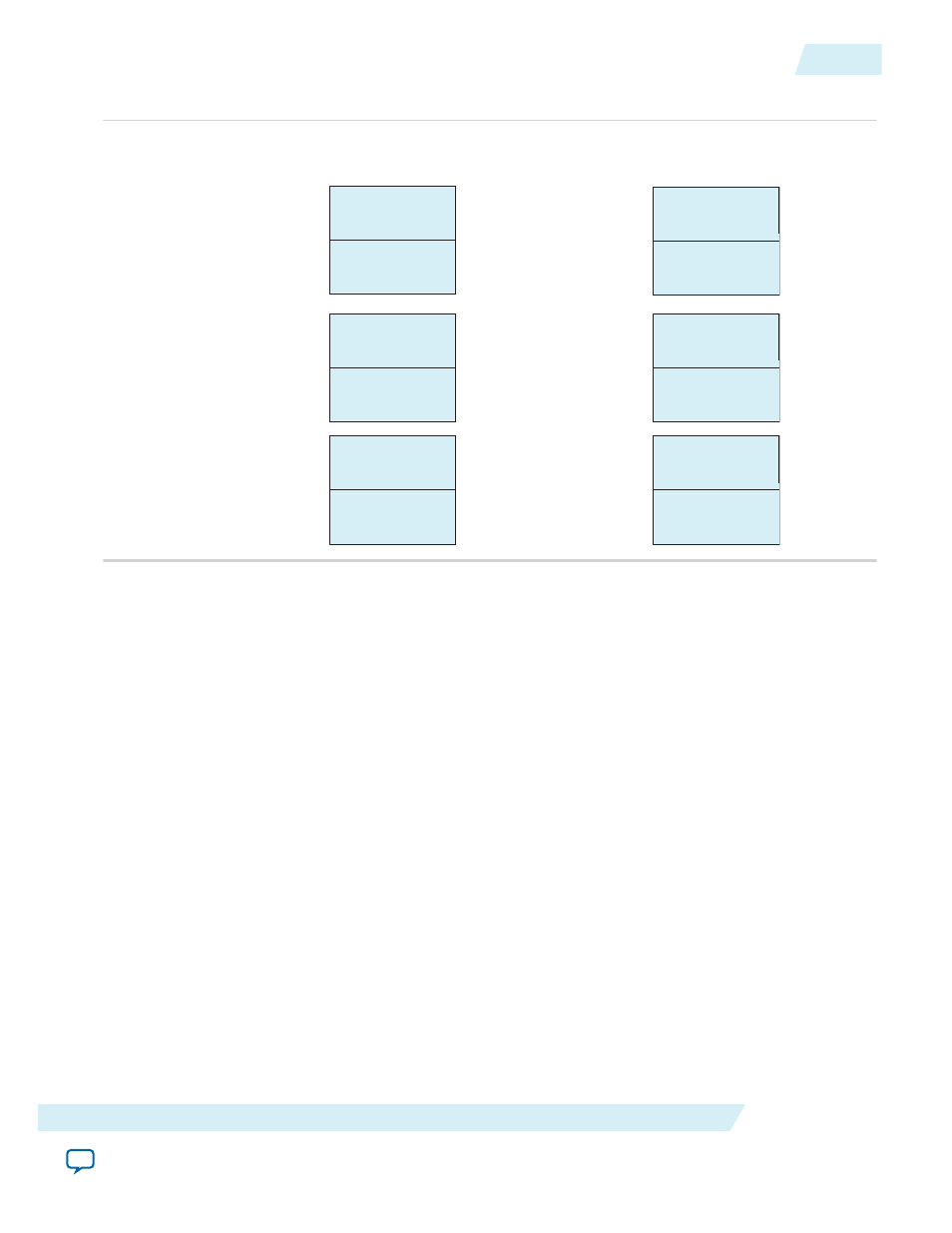

Figure 6-11: Layout of Data with 4 Dword Headers

Header 1 [63:32]

Cycle 1

Data Unaligned to

QWord Boundary

Data Aligned to

QWord Boundary

Cycle 2

Header 0 [31:0]

Header 3[63:32]

Header 2 [31:0]

Data [63:32]

Header 1 [63:32]

Header 0 [31:0]

Header 2 [31:0]

Cycle 1

Cycle 2

Cycle 3

Cycle 3

Data [31:0]

Unused, but must

be written

Unused, but must

be written

Header 3[63:32]

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

Register 1

Register 0

The TX TLP programming model scales with the data width. The Application Layer performs the same

writes for both the 64- and 128-bit interfaces. The Application Layer can only have one outstanding non-

posted request at a time. The Application Layer must use tags 16–31 to identify non-posted requests.

Note: For Root Ports, the Avalon-MM bridge does not filter Type 0 Configuration Requests by device

number. Application Layer software should filter out all requests to Avalon-MM Root Port

registers that are not for device 0. Application Layer software should return an Unsupported

Request Completion Status.

Sending a Write TLP

The Application Layer performs the following sequence of Avalon-MM accesses to the CRA slave port to

send a Memory Write Request:

1. Write the first 32 bits of the TX TLP to

RP_TX_REG0.

2. Write the next 32 bits of the TX TLP to

RP_TX_REG1.

3. Write the

RP_TX_CNTRL.SOP

to 1’b1 to push the first two dwords of the TLP into the Root Port TX

FIFO.

4. Repeat Steps 1 and 2. The second write to

RP_TX_REG1

is required, even for three dword TLPs with

aligned data.

5. If the packet is complete, write

RP_TX_CNTRL

to 2’b10 to indicate the end of the packet. If the packet is

not complete, write 2’b00 to

RP_TX_CNTRL.

6. Repeat this sequence to program a complete TLP.

When the programming of the TX TLP is complete, the Avalon-MM bridge schedules the TLP with

higher priority than TX TLPs coming from the TX slave port.

UG-01145_avmm

2015.05.14

Sending a Write TLP

6-27

Registers

Altera Corporation