Altera Arria V Hard IP for PCI Express User Manual

Page 105

Chapter 7: IP Core Interfaces

7–7

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

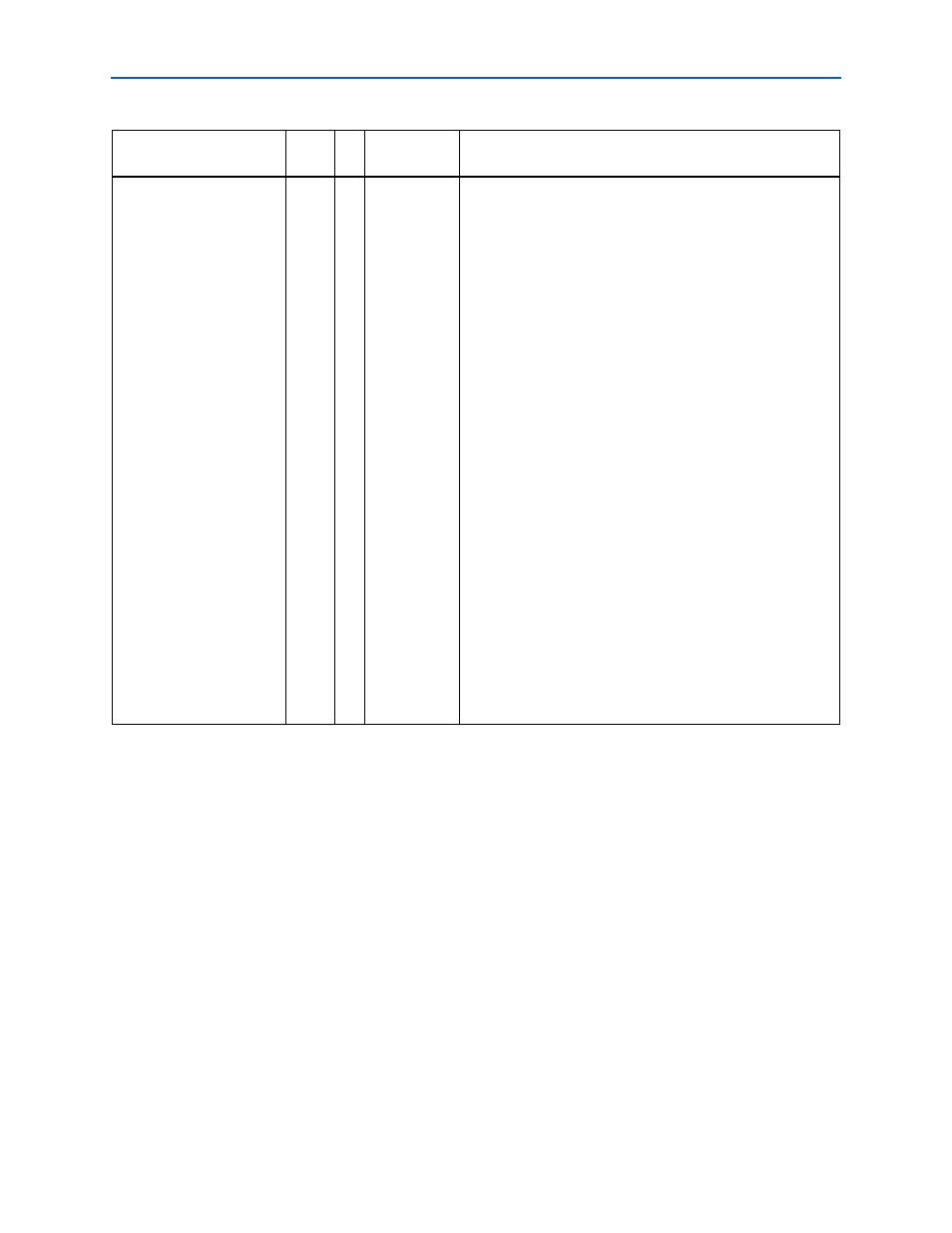

rx_st_bar

8

O

component

specific

The decoded BAR bits for the TLP. Valid for

MRd

,

MWr

,

IOWR

, and

IORD

TLPs; ignored for the completion or message TLPs. Valid

during the cycle in which

rx_st_sop

illustrates the timing of this signal for 64-bit data.

Figure 7–10

illustrates the timing of this signal for 128-bit data.

The following encodings are defined for Endpoints:

■

Bit 0: BAR 0

■

Bit 1: BAR 1

■

Bit 2: Bar 2

■

Bit 3: Bar 3

■

Bit 4: Bar 4

■

Bit 5: Bar 5

■

Bit 6: Expansion ROM

■

Bit 7: Reserved

The following encodings are defined for Root Ports:

■

Bit 0: BAR 0

■

Bit 1: BAR 1

■

Bit 2: Primary Bus number

■

Bit 3: Secondary Bus number

■

Bit 4: Secondary Bus number to Subordinate Bus number

window

■

Bit 5: I/O window

■

Bit 6: Non-Prefetchable window

■

Bit 7: Prefetchable window

Table 7–3. 64- or 128-Bit Avalon-ST RX Datapath (Part 3 of 4)

Signal

Width

Dir

Avalon-ST

Type

Description