Altera Arria V Hard IP for PCI Express User Manual

Page 182

9–2

Chapter 9: Reset and Clocks

Reset

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

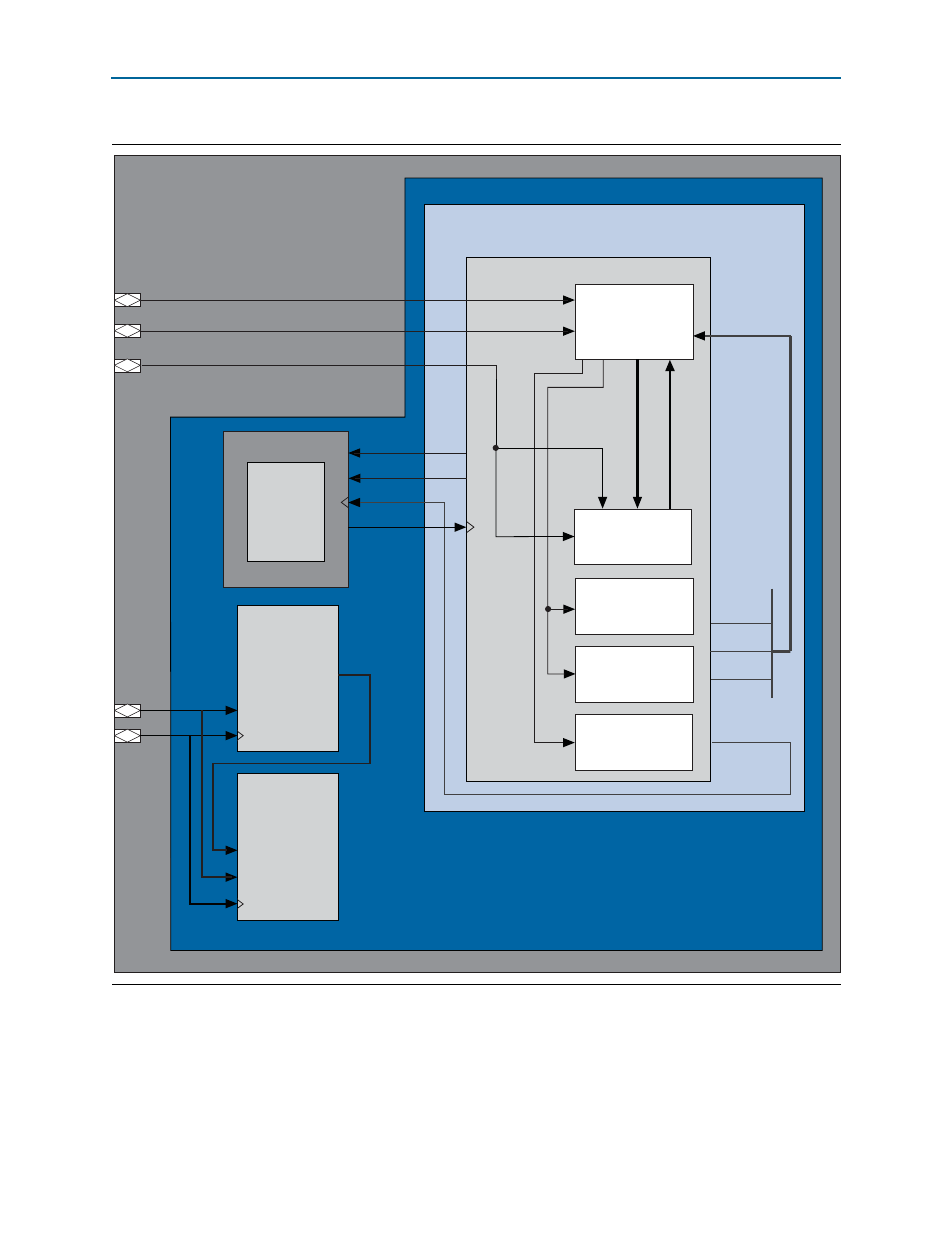

Figure 9–1. Reset Controller

Example Design

altpcie_dev_hip_ast_hwtcl.v

altpcied_<dev>_hwtcl.sv

Transceiver Hard

Reset Logic/Soft Reset

Controller

Configuration Space

Sticky Registers

Datapath State

Machines of

Hard IP Core

SERDES

Configuration Space

Non-Sticky Registers

reset_status

pld_clk

pin_perstn

npor

refclk

srst

crst

l2_exit

hotrst_exit

dlup_exit

pld_clk_inuse

Hard IP for PCI Express

fixed_clk

(100 or 125 MHz)

reconfig_xcvr_clk

mgmt_rst_reset

reconfig_busy

Transceiver

Reconfiguration

Controller

reconfig_xcvr_clk

reconfig_busy

reconfig_xcvr_rst

pcie_reconfig_

driver_0

altpcie_<dev>_hip_256_pipen1b.v

altpcie_rs_serdes.v

coreclkout_hip

coreclkout_hip

top.v

tx_digitalrst

rx_analogrst

rx_digitalrst

rx_freqlock

rx_signaldetect

rx_pll_locked

pll_locked

tx_cal_busy

rx_cal_busy

Chaining

DMA

(APPs)

reconfig_clk

mgmt_rst_reset