Altera Arria V Hard IP for PCI Express User Manual

Page 129

Chapter 7: IP Core Interfaces

7–31

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

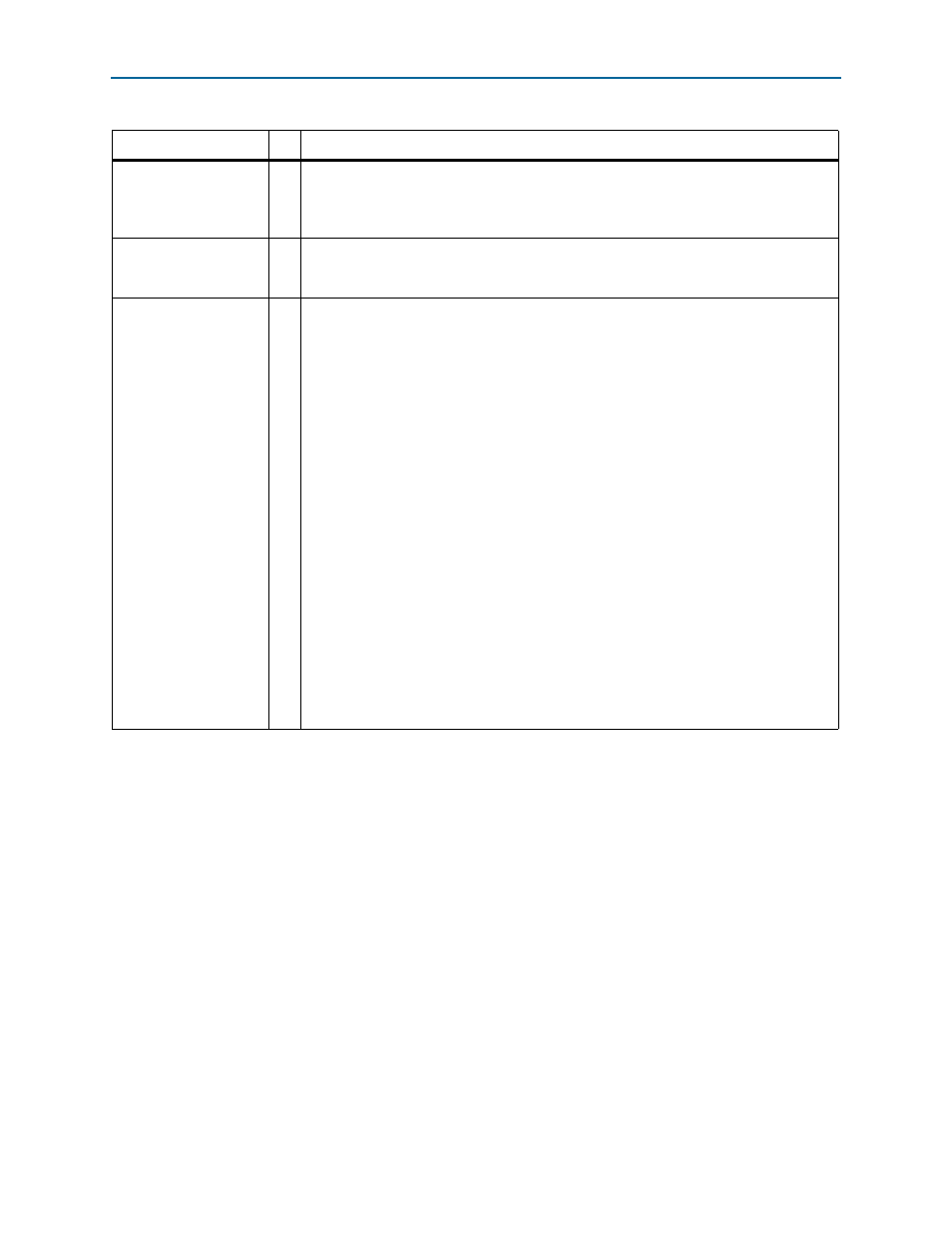

tl_cfg_sts[122:0]

0

Configuration status bits. This information updates every

pld_clk

cycle. Bits[52:0] record

status information for function0. Bits[62:53] record information for function1. Bits[72:63]

record information for function 2, and so on. Refer to

Table 7–12

for a detailed description

of the status bits.

tl_cfg_sts_wr

0

Write signal. This signal toggles when

tl_cfg_sts

has been updated (every 8

core_clk

cycles). The toggle marks the edge where

tl_cfg_sts

data changes. You can use this

edge as a reference to determine when the data is safe to sample.

tl_hpg_ctrl_er[4:0]

I

The tl_

hpg_ctrl_er

signals are only available in Root Port mode and when the Slot

Capability register is enabled. Refer to the

parameter in

. For Endpoint variations the

tl_hpg_ctrl_er

input should be hardwired to 0s.

The bits have the following meanings:

■

[0]: Attention button pressed. This signal should be asserted when the attention button

is pressed. If no attention button exists for the slot, this bit should be hardwired to 0,

and the

Attention Button Present

bit (bit[0]) in the Slot Capability register is set

to 0.

■

[1]: Presence detect. This signal should be asserted when a presence detect circuit

detects a presence change in the slot.

■

[2]: Manually-operated retention latch (MRL) sensor changed. This signal should be

asserted when an MRL sensor indicates that the MRL is Open. If an MRL Sensor does

not exist for the slot, this bit should be hardwired to 0, and the

MRL

Sensor

Present

bit

(bit[2]) in the Slot Capability register is to 0.

■

[3]:Power fault detected. This signal should be asserted when the power controller

detects a power fault for this slot. If this slot has no power controller, this bit should be

hardwired to 0, and the

Power

Controller

Present

bit (bit[1]) in the Slot Capability

register is set to 0.

■

[4]: Power controller status. This signal is used to set the command completed bit of

the

Slot

Status

register. Power controller status is equal to the power controller

control signal. If this slot has no power controller, this bit should be hardwired to 0 and

the

Power Controller Present

bit (bit[1]) in the Slot Capability register is set to 0.

Table 7–11. Configuration Space Signals (Hard IP Implementation) (Part 2 of 2)

Signal

Dir

Description