Altera Arria V Hard IP for PCI Express User Manual

Page 91

Chapter 6: IP Core Architecture

6–17

Avalon-MM Bridge TLPs

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

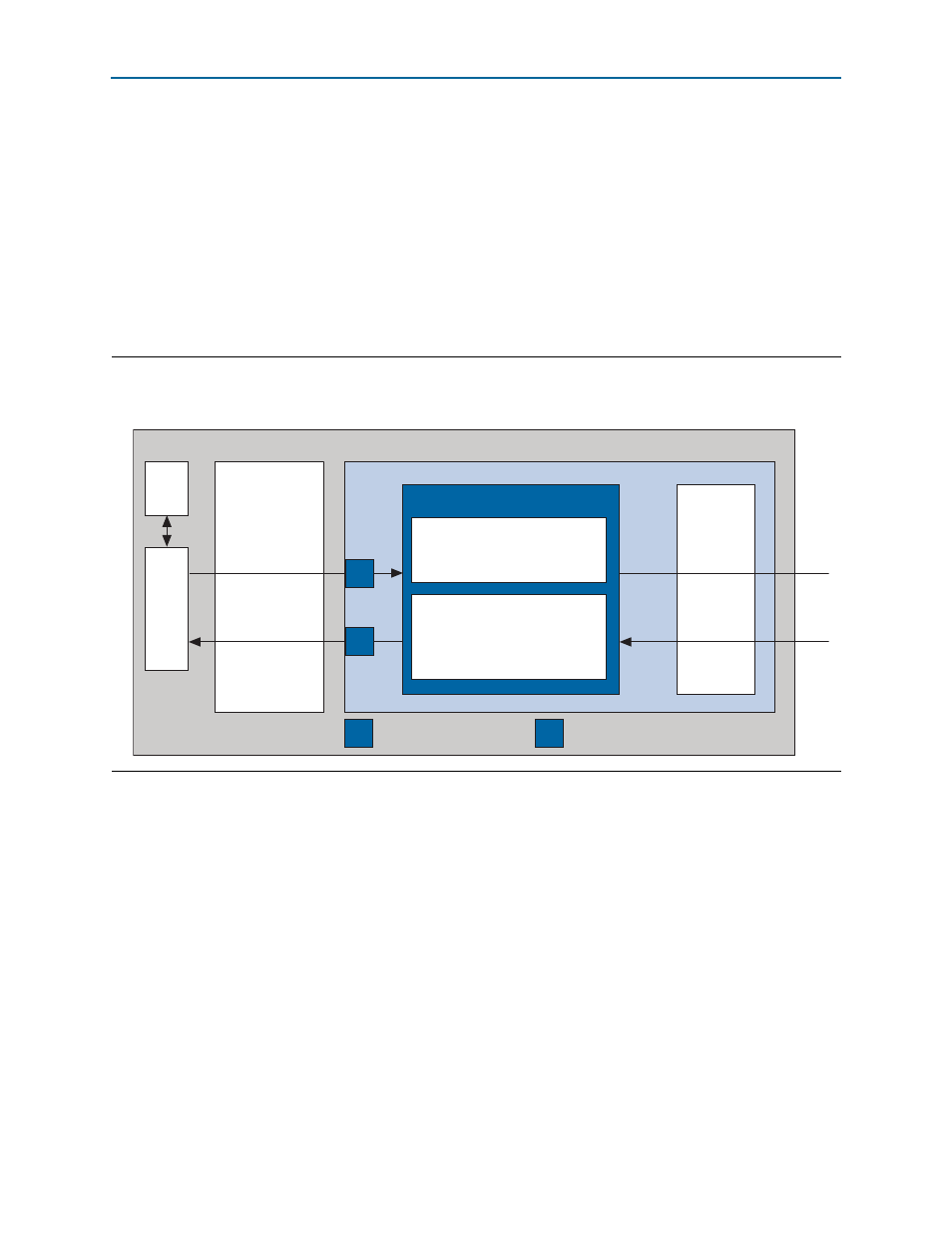

PCI Express-to-Avalon-MM Address Translation for Endpoints

The PCI Express Avalon-MM Bridge translates the system-level physical addresses,

typically up to 64 bits, to the significantly smaller addresses used by the Application

Layer’s Avalon-MM slave components. You can specify up to six BARs for address

translation when you customize your Hard IP for PCI Express as described in

Address Registers for Function <n>” on page 4–8

. The PCI Express Avalon-MM

Bridge also translates the Application Layer addresses to system-level physical

addresses as described in

“Avalon-MM-to-PCI Express Address Translation

.

Figure 6–7

provides a high-level view of address translation in both directions.

1

When configured as a Root Port, a single RX Avalon-MM master forwards all RX TLPs

to the Qsys interconnect.

The Avalon-MM RX master module port has an 8-byte datapath in 64-bit mode and a

16-byte datapath in 128-bit mode. The Qsys interconnect fabric manages mismatched

port widths transparently.

As Memory Request TLPs are received from the PCIe link, the most significant bits are

used in the BAR matching as described in the PCI specifications. The least significant

bits not used in the BAR match process are passed unchanged as the Avalon-MM

address for that BAR's RX Master port.

For example, consider the following configuration specified using the Base Address

Registers in the GUI.

1. BAR1:0 is a 64-bit prefetchable memory that is 4KBytes -12 bits

Figure 6–7. Address Translation in TX and RX Directions

Transaction,

Data Link,

and PHY

DMA

Avalon-MM

32-Bit Byte Address

Avalon-MM

32-Bit Byte Address

PCIe TLP

Address

PCIe TLP

Address

Qsys Generated Endpoint with DMA Controller and On-Chip RAM

TX

PCIe

Link

RX

PCIe

Link

PCI Express Avalon-MM Bridge

Interconnect

Avalon-MM Hard IP for PCI Express

Number of address pages (1-512)

Size of address pages

Address Translation Table Parameters

Avalon-MM-to-PCIe Address Translation

BAR (0-5)

BAR Type

BAR Size

PCI Base Address Registers (BAR)

PCIe-to-Avalon-MM Address Translation

On-

Chip

RAM

M

S

= RX Avalon-MM Master

= TX Avalon-MM Slave

S

M