Avalon memory-mapped system settings, Avalon memory-mapped system settings –9 – Altera Arria V Hard IP for PCI Express User Manual

Page 73

Chapter 5: Parameter Settings for the Avalon-MM Arria V Hard IP for PCI Express

5–9

Avalon Memory-Mapped System Settings

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Avalon Memory-Mapped System Settings

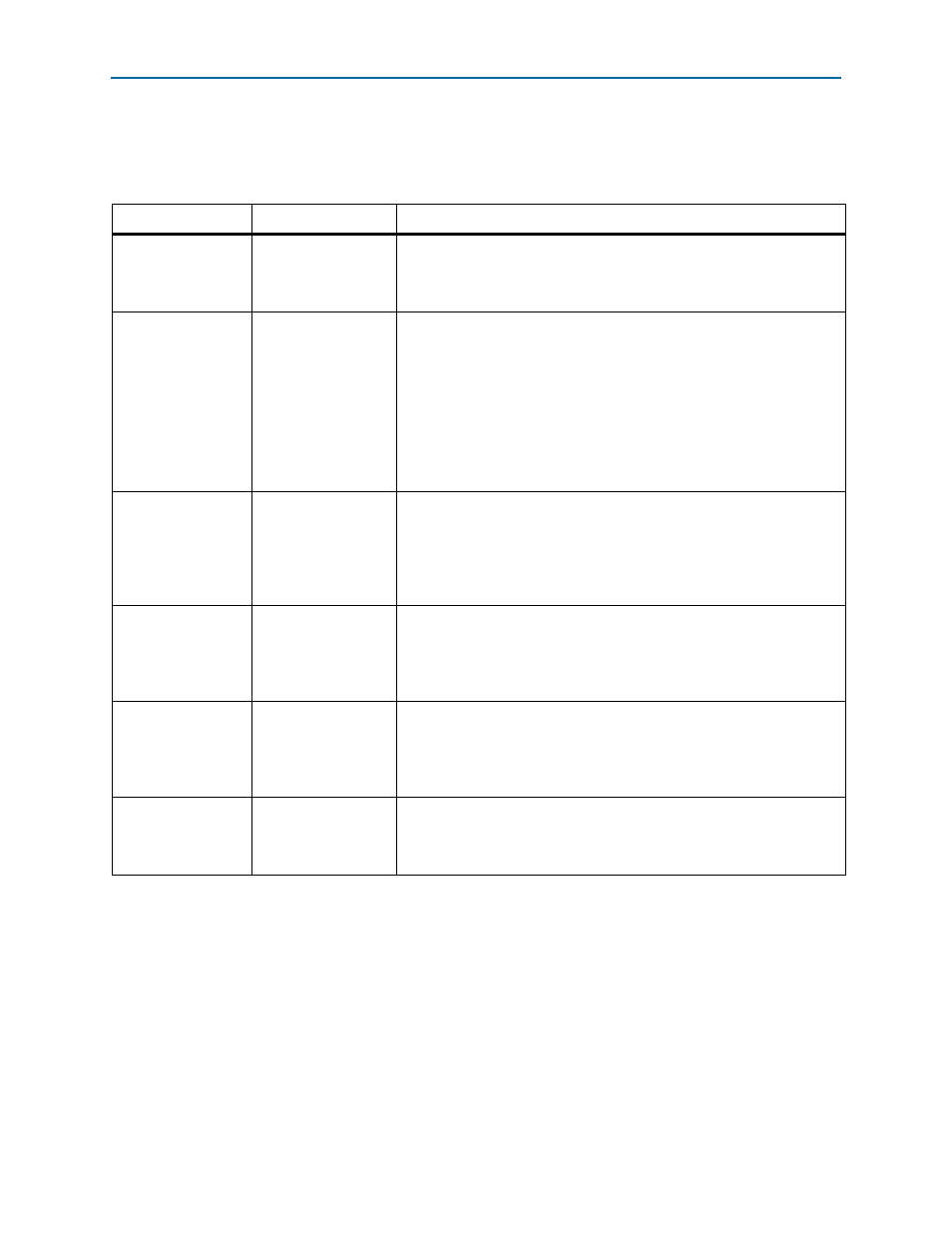

Table 5–10

lists the Avalon-MM system parameter registers.

Table 5–10. Avalon Memory-Mapped System Settings

Parameter

Value

Description

Avalon-MM data

width

64-bit

128-bit

Specifies the interface width between the PCI Express Transaction Layer

and the Application Layer. Refer to

comprehensive list of available link width, interface width, and frequency

combinations.

Peripheral Mode

Requester/Completer,

Completer-Only

Specifies whether the Avalon-MM Arria V Hard IP for PCI Express is

capable of sending requests to the upstream PCI Express devices.

Requester/Completer—In this mode, the Hard IP can send request

packets on the PCI Express TX link and receive request packets on the

PCI Express RX link.

Completer-Only—In this mode, the Hard IP can receive requests, but

cannot initiate upstream requests. However, it can transmit completion

packets on the PCI Express TX link. This mode removes the Avalon-MM

TX slave port and thereby reduces logic utilization.

Single DW completer

On/Off

This is a non-pipelined version of Completer-Only mode. At any time, only

a single request can be outstanding. Single dword completer uses fewer

resources than Completer-Only. This variant is targeted for systems that

require simple read and write register accesses from a host CPU. If you

select this option, the width of the data for RXM BAR masters is always 32

bits, regardless of the Avalon-MM width.

Control Register

Access (CRA)

Avalon-MM slave

port

On/Off

Allows read and write access to bridge registers from the interconnect

fabric using a specialized slave port. This option is required for

Requester/Completer variants and optional for Completer-Only variants.

Enabling this option allows read and write access to bridge registers. This

option is not available for the Single dword completer.

Enable multiple

MSI/MSI-X support

On/Off

When you turn this option On, the core includes top-level MSI and MSI-X

interfaces that you can use to implement a Customer Interrupt Handler for

MSI and MSI-X interrupts. For more information about the Custom

Interrupt Handler, refer to

Interrupts for End Points Using the Avalon-MM

Interface with Multiple MSI/MSI-X Support

Auto Enable PCIe

interrupt (enabled at

power-on)

On/Off

Turning on this option enables the Avalon-MM Arria V Hard IP for PCI

Express interrupt register at power-up. Turning off this option disables the

interrupt register at power-up. The setting does not affect run-time

configuration of the interrupt enable register.