Altera Arria V Hard IP for PCI Express User Manual

Page 45

Chapter 3: Getting Started with the Avalon-MM Arria Hard IP for PCI Express

3–11

Simulating the Example Design

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

4. After Qsys reports Generate Completed in the Generate progress box title, click

Close

.

5. On the File menu, click Save. and type the file name

ep_g1x4.qsys

.

Table 3–14

lists the directories that are generated in your Quartus II project directory.

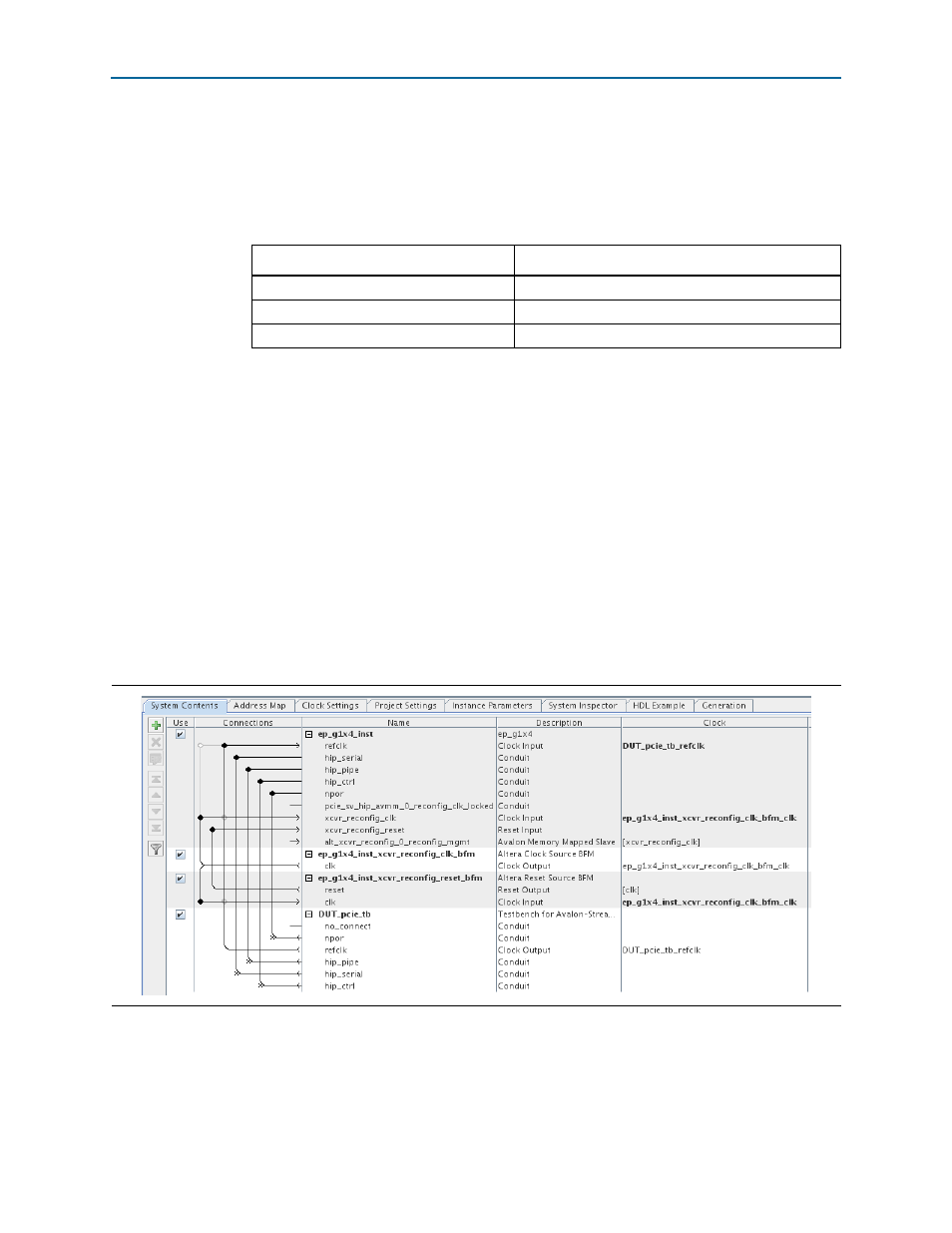

Qsys creates a top-level testbench named

<project_dir>/

ep_g1x4/testbench/

ep_g1x4_tb.qsys.

This testbench connects an appropriate BFM to each exported

interface. Qsys generates the required files and models to simulate your PCI Express

system.

The simulation of the design example uses the following components and software:

■

The system you created using Qsys

■

A testbench created by Qsys in the

<project_dir>/

ep_g1_x4/testbench

directory. You

can view this testbench in Qsys by opening

<project_dir>/

ep_g1_x4/testbench/

s5_avmm_tb.qsys

which shown in

Figure 3–2

.

■

The ModelSim software

1

You can also use any other supported third-party simulator to simulate your design.

Qsys creates IP functional simulation models for all the system components. The IP

functional simulation models are the .vo or .vho files generated by Qsys in your

project directory.

Table 3–14. Qsys System Generated Directories

Directory

Location

Qsys system

<project_dir>/ep_g1x4

Testbench

<project_dir>/ep_g1x4/testbench

Synthesis

<project_dir>/ep_g1x4/synthesis

Figure 3–2. Qsys Testbench for the PCI Example Design