Altera Arria V Hard IP for PCI Express User Manual

Page 183

Chapter 9: Reset and Clocks

9–3

Reset

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

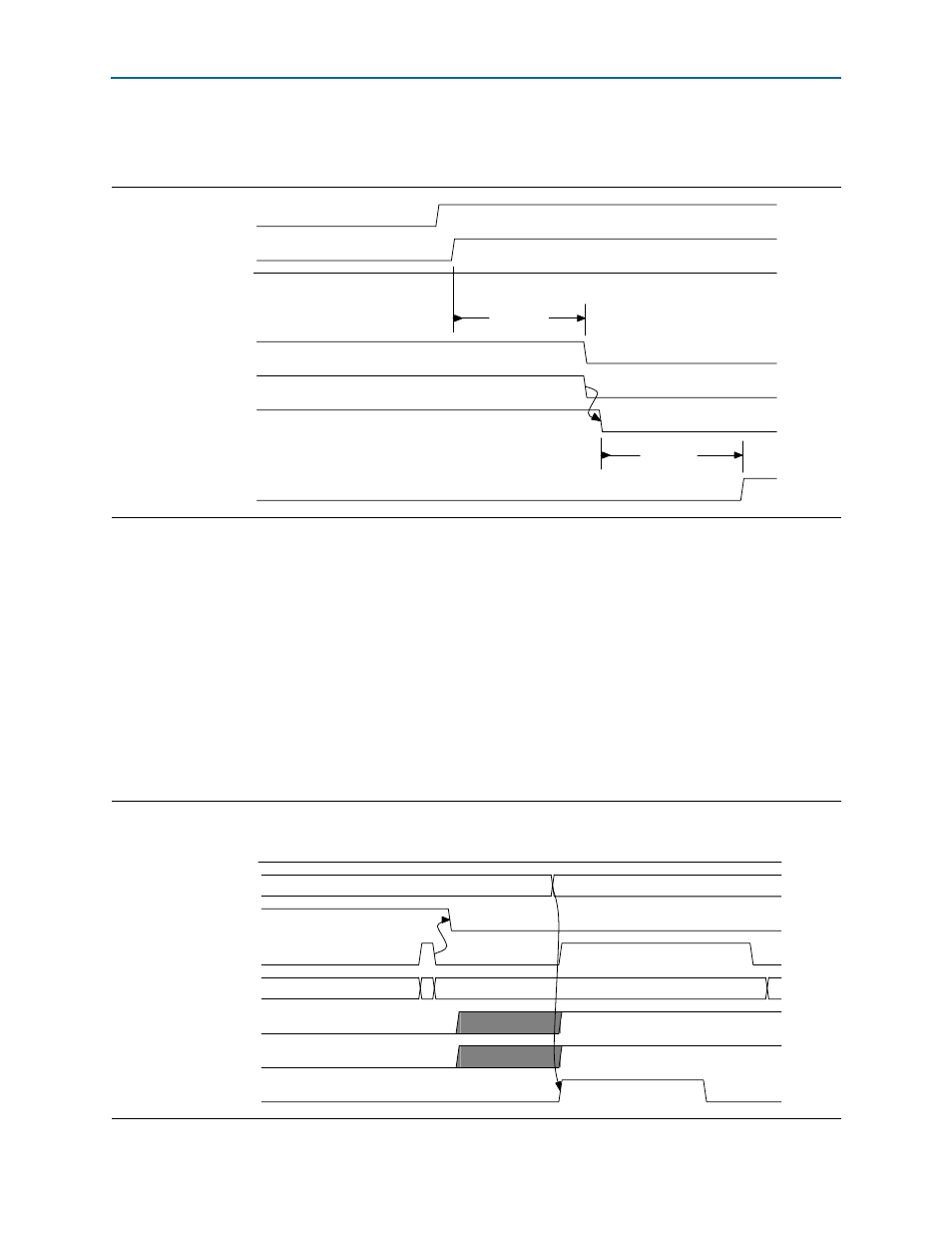

Figure 9–2

illustrates the reset sequence for the Hard IP for PCI Express IP core and

the Application Layer logic.

As

Figure 9–2

illustrates, this reset sequence includes the following steps:

1. After

pin_perstn

or npor is released, the Hard IP soft reset controller waits for

pld_clk_inuse

to be asserted.

2.

csrt

and

srst

are released 32 cycles after

pld_clk_inuse

is asserted.

3. The Hard IP for PCI Express deasserts the

reset_status

output to the Application

Layer.

4. The Application Layer deasserts

app_rstn

32 cycles after

reset_status

is

released.

Figure 9–3

illustrates the RX transceiver reset sequence.

Figure 9–2. Hard IP for PCI Express and Application Logic Rest Sequence

pin_perstn

pld_clk_inuse

serdes_pll_locked

crst

32 cycles

32 cycles

srst

reset_status

app_rstn

Figure 9–3. RX Transceiver Reset Sequence

rx_pll_locked

rx_analogreset

ltssmstate[4:0]

txdetectrx_loopback

pipe_phystatus

pipe_rxstatus[2:0]

rx_signaldetect

rx_freqlocked

rx_digitalreset

3

0

01