Specifying address assignments, Simulating the example design – Altera Arria V Hard IP for PCI Express User Manual

Page 44

3–10

Chapter 3: Getting Started with the Avalon-MM Arria Hard IP for PCI Express

Specifying Address Assignments

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Specifying Address Assignments

Qsys requires that you resolve the base addresses of all Avalon-MM slave interfaces in

the Qsys system. You can either use the auto-assign feature, or specify the base

addresses manually. To use the auto-assign feature, on the System menu, click Assign

Base Addresses

. In the design example, you assign the base addresses manually.

The Avalon-MM Arria Hard IP for PCI Express assigns base addresses to each BAR.

The maximum supported BAR size is 4 GByte, or 32 bits.

Follow these steps to assign a base address to an Avalon-MM slave interface

manually:

1. In the row for the Avalon-MM slave interface base address you want to specify,

click the Base column.

2. Type your preferred base address for the interface.

3. Assign the base addresses listed in

Table 3–13

.

The following figure illustrates the complete system.

For this example BAR1:0 is 22 bits or 4 MBytes. This BAR accesses Avalon addresses

from 0x00200000– 0x00200FFF. BAR2 is 15 bits or 32 KBytes. BAR2 accesses the DMA

control_port_slave at offsets 0x00004000 through 0x0000403F. The pci_express

CRA

slave port is accessible at offsets 0x0000000–0x0003FFF from the programmed BAR2

base address. For more information on optimizing BAR sizes, refer to

“Minimizing

BAR Sizes and the PCIe Address Space” on page 7–21

.

Simulating the Example Design

Follow these steps to generate the files for the testbench and synthesis.

1. On the Generation tab, in the Simulation section, set the following options:

a. For Create simulation model, select None. (This option allows you to create a

simulation model for inclusion in your own custom testbench.)

b. For Create testbench Qsys system, select Standard, BFMs for standard

Avalon interfaces

.

c. For Create testbench simulation model, select Verilog.

2. In the Synthesis section, turn on Create HDL design files for synthesis.

3. Click the Generate button at the bottom of the tab.

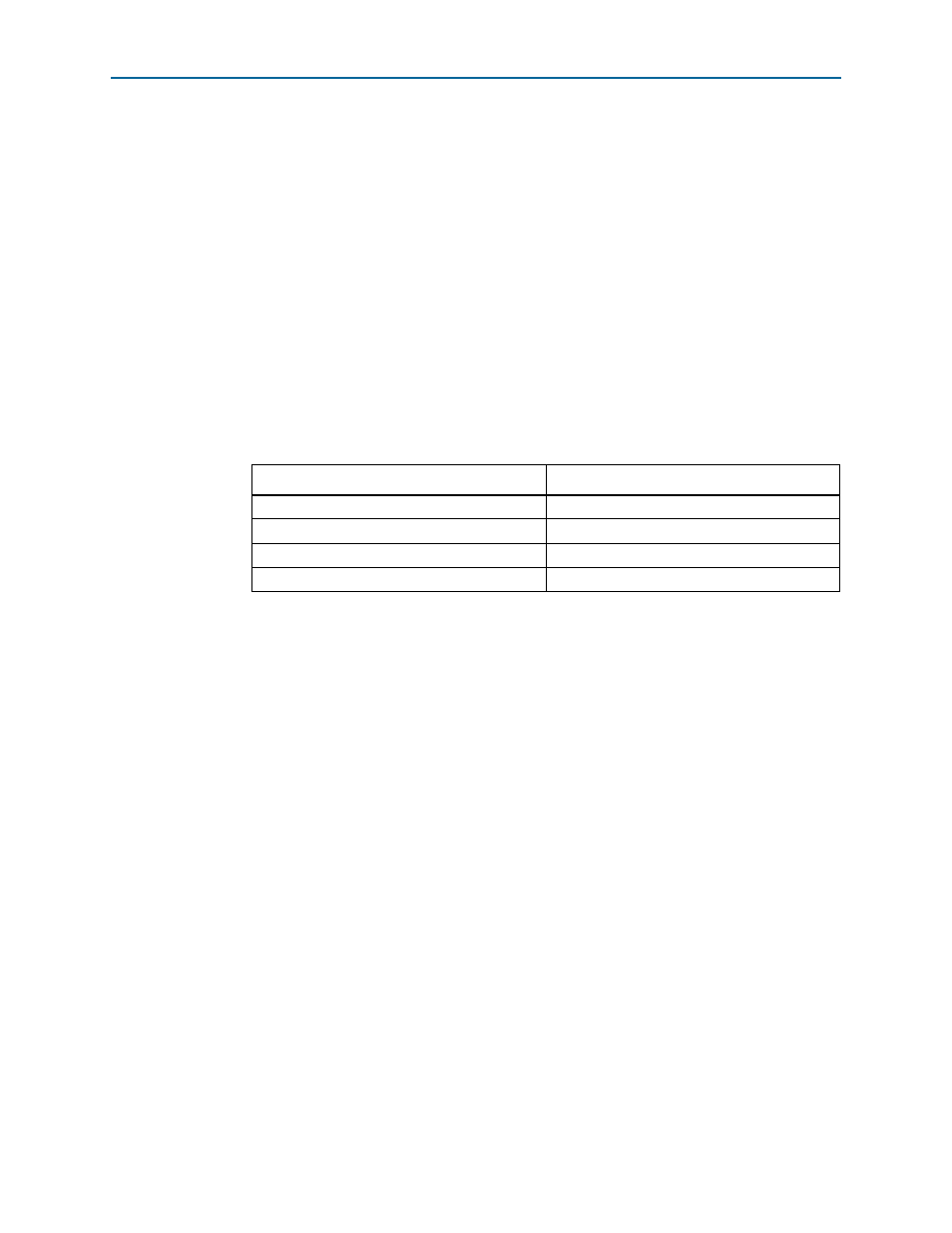

Table 3–13. Base Address Assignments for Avalon-MM Slave Interfaces

Interface Name

Exported Name

DUT

Txs

0x00000000

DUT

Cra

0x00000000

DMA

control_port_slave

0x00004000

onchip_memory_0

s1

0x00200000