Altera Arria V Hard IP for PCI Express User Manual

Page 160

8–6

Chapter 8: Register Descriptions

Altera-Defined Vendor Specific Extended Capability (VSEC)

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Table 8–10

defines the fields of the

Vendor Specific Extended Capability Header

register.

Table 8–11

defines the fields of the

Altera-Defined Vendor Specific

register. You

can specify these fields when you instantiate the Hard IP; they are read-only at

run-time.

Table 8–12

defines the

Altera Marker

register.

Table 8–13

defines the

JTAG Silicon ID

registers.

Table 8–14

defines the

User Device or Board Type ID

register.

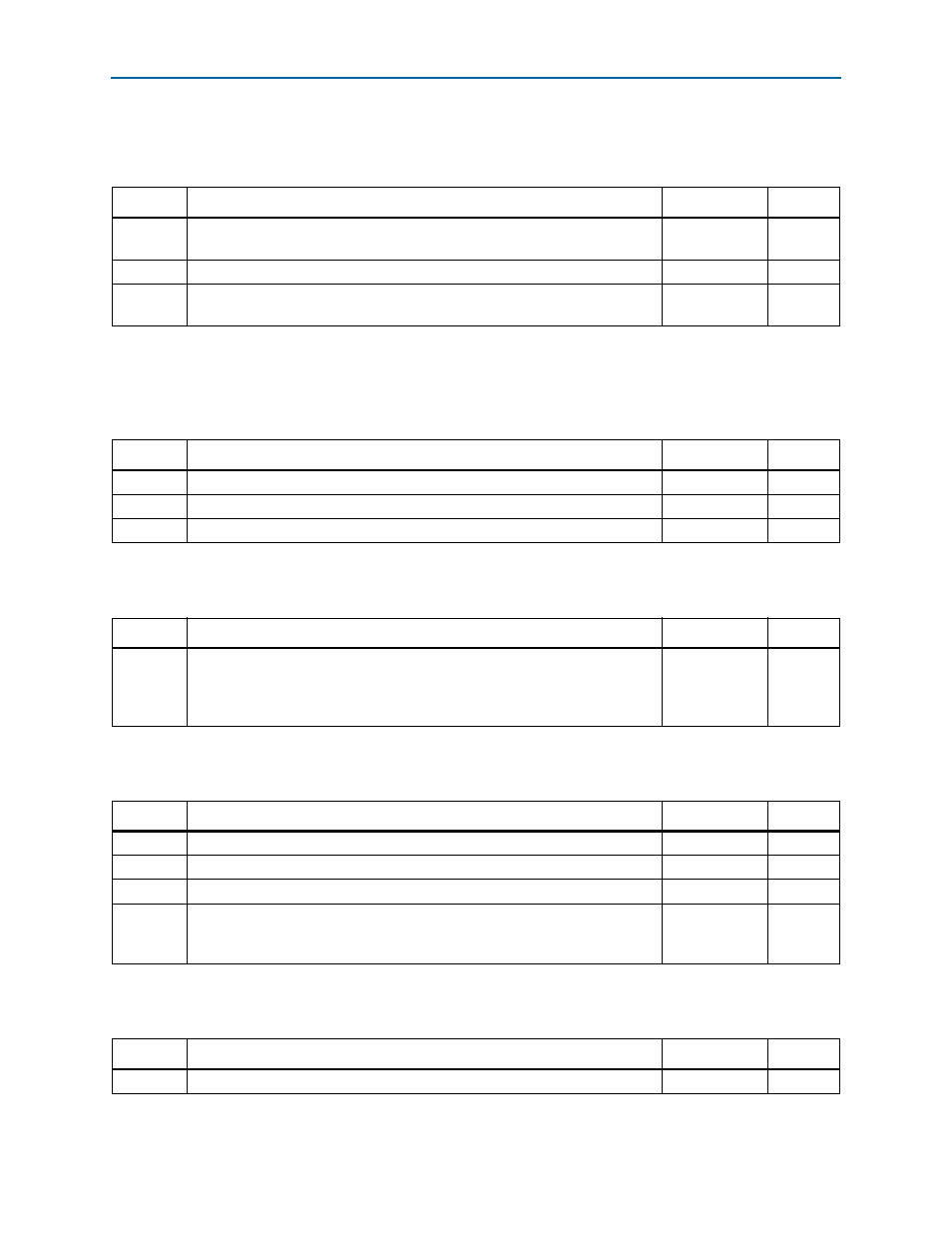

Table 8–10.

Altera-Defined VSEC Capability Header

Bits

Register Description

Value

Access

[15:0]

PCI Express Extended Capability ID

. PCIe specification defined value

for VSEC Capability ID.

0x000B

RO

[19:16]

Version

. PCIe specification defined value for VSEC version.

0x1

RO

[31:20]

Next Capability Offset

. Starting address of the next Capability Structure

implemented, if any.

Variable

RO

Table 8–11.

Altera-Defined Vendor Specific Header

Bits

Register Description

Value

Access

[15:0]

VSEC ID

. A user configurable VSEC ID.

User entered

RO

[19:16]

VSEC Revision

. A user configurable VSEC revision.

Variable

RO

[31:20]

VSEC Length

. Total length of this structure in bytes.

0x044

RO

Table 8–12. Altera Marker

Bits

Register Description

Value

Access

[31:0]

Altera Marker

. This read only register is an additional marker. If you use the

standard Altera Programmer software to configure the device with CvP, this

marker provides a value that the programming software reads to ensure that it

is operating with the correct VSEC.

A Device Value

RO

Table 8–13. JTAG Silicon ID

Bits

Register Description

Value

Access

[127:96]

JTAG Silicon ID DW3

TBD

RO

[95:64]

JTAG Silicon ID DW2

TBD

RO

[63:32]

JTAG Silicon ID DW1

TBD

RO

[31:0]

JTAG Silicon ID DW0

- This is the JTAG Silicon ID that CvP programming

software reads to determine to that the correct SRAM object file (.sof) is being

used.

TBD

RO

Table 8–14. User Device or Board Type ID

Bits

Register Description

Value

Access

[15:0]

Configurable device or board type ID to specify to CvP the correct .sof. Variable

RO