Altera Arria V Hard IP for PCI Express User Manual

Page 179

Chapter 8: Register Descriptions

8–25

Correspondence between Configuration Space Registers and the PCIe Spec 2.1

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

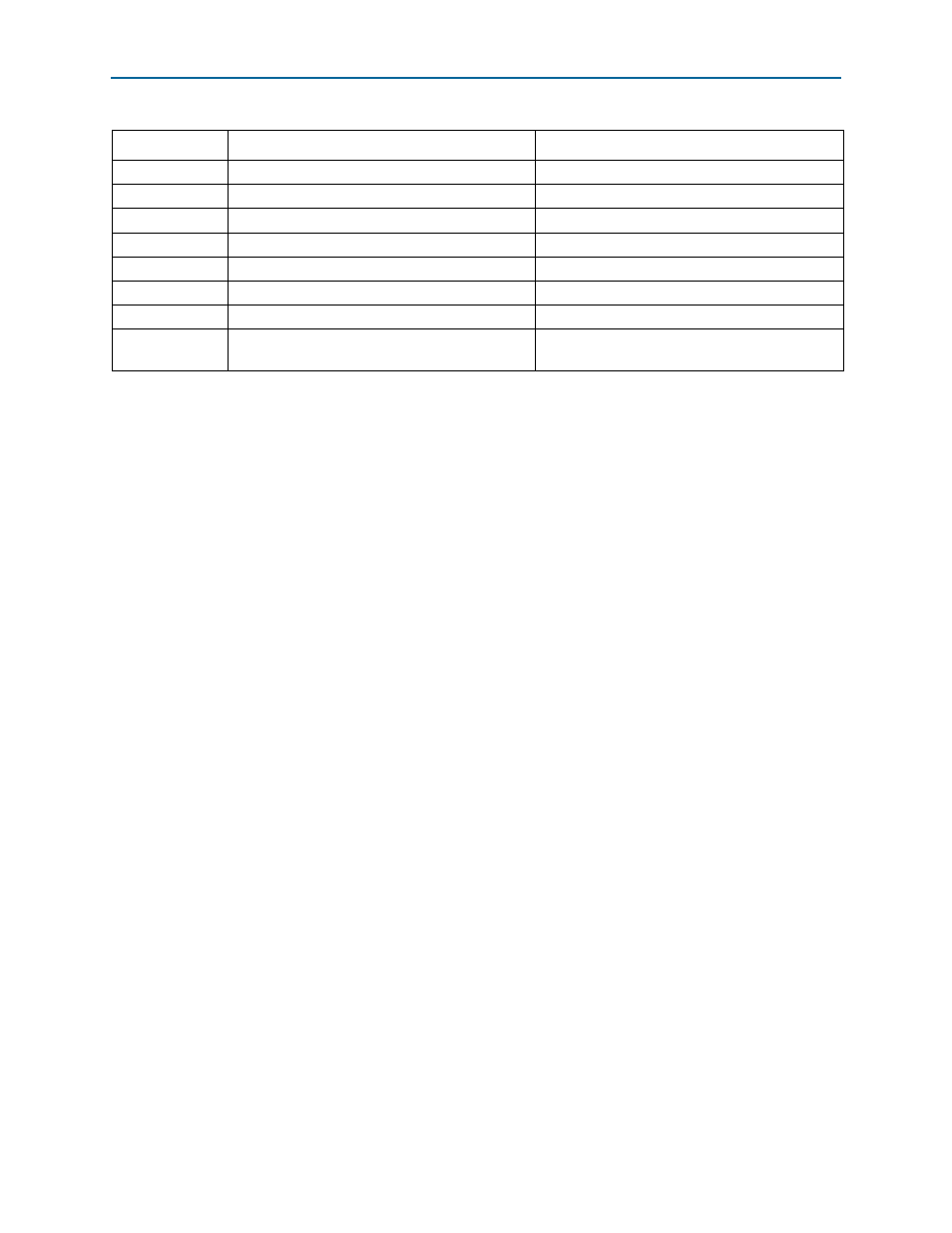

0x80C

Uncorrectable Error Severity Register

Uncorrectable Error Severity Register

0x810

Correctable Error Status Register

Correctable Error Status Register

0x814

Correctable Error Mask Register

Correctable Error Mask Register

0x818

Advanced Error Capabilities and Control Register

Advanced Error Capabilities and Control Register

0x81C

Header Log Register

Header Log Register

0x82C

Root Error Command

Root Error Command Register

0x830

Root Error Status

Root Error Status Register

0x834

Error Source Identification Register Correctable

Error Source ID Register

Error Source Identification Register

Table 8–39. Correspondence Configuration Space Registers and PCIe Base Specification Rev. 2.1 (Part 4 of 4)

Byte Address

Hard IP Configuration Space Register

Corresponding Section in PCIe Specification