Altera Arria V Hard IP for PCI Express User Manual

Page 162

8–8

Chapter 8: Register Descriptions

Altera-Defined Vendor Specific Extended Capability (VSEC)

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Table 8–17

defines the

CvP Data

register. Programming software should write the

configuration data to this register. Every write to this register sets the data output to

the FPGA control block and generates <n> clock cycles to the FPGA control block as

specified by the

CVP_NUM_CLKS

field in the

CvP Mode

Control

register. Software must

ensure that all bytes in the memory write dword are enabled. You can access this

register using configuration writes, alternatively, when in CvP mode, this register can

also be written by a memory write to any address defined by a memory space BAR for

this device. Using memory writes should allow for higher throughput than

configuration writes.

Table 8–18

defines the

CvP Programming Control

register. This register is written by

the programming software to control CvP programming.

f

Refer to

for

more information about using CvP.

[1]

HIP_CLK_SEL

. Selects between PMA and fabric clock when

USER_MODE

= 1 and

PLD_CORE_READY

= 1. The following encodings are defined:

■

1: Selects internal clock from PMA which is required for CVP_MODE

■

0: Selects the clock from soft logic fabric. This setting should only be used

when the fabric is configured in

USER_MODE

with a configuration file that

connects the correct clock.

To ensure that there is no clock switching during CvP, you should only change

this value when the Hard IP for PCI Express has been idle for 10

μ

s and wait

10

μ

s after changing this value before resuming activity.

1’b0

RW

[0]

CVP_MODE

. Controls whether the HIP is in CVP_MODE or normal mode. The

following encodings are defined:

■

1: CVP_MODE is active. Signals to the FPGA control block active and all TLPs

are routed to the Configuration Space. This

CVP_MODE

cannot be enabled if

CVP_EN

= 0.

■

0: The IP core is in normal mode and TLPs are route to the FPGA fabric.

1’b0

RW

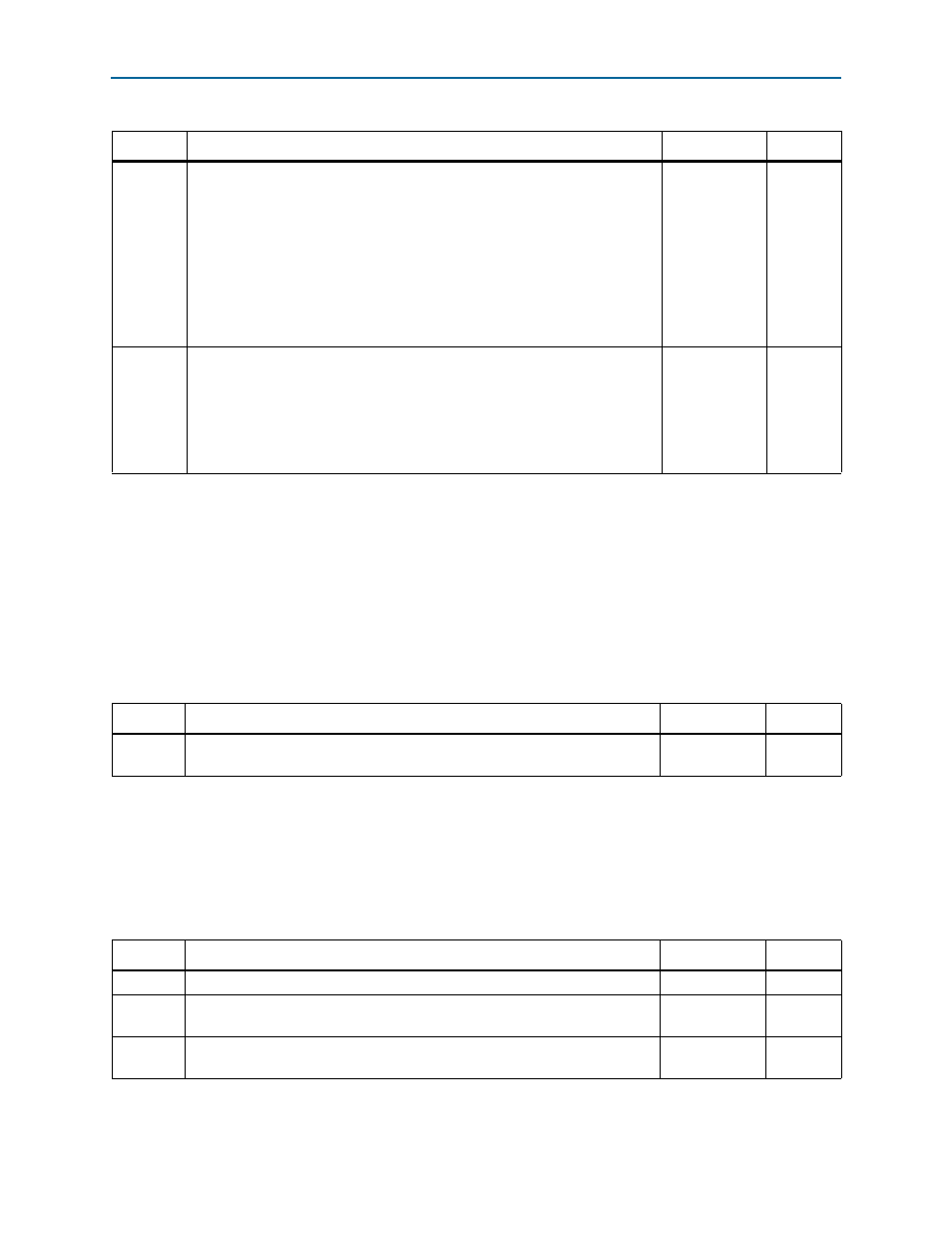

Table 8–16. CvP Mode Control (Part 2 of 2)

Bits

Register Description

Reset Value

Access

Table 8–17. CvP Data Register

Bits

Register Description

Reset Value

Access

[31:0]

Configuration data to be transferred to the FPGA control block to configure the

device.

0x00000000

RW

Table 8–18. CvP Programming Control Register

Bits

Register Description

Reset Value

Access

[31:2]

Reserved.

0x0000

RO

[1]

START_XFER

. Sets the CvP output to the FPGA control block indicating the start

of a transfer.

1’b0

RW

[0]

CVP_CONFIG

. When asserted, instructs that the FPGA control block begin a

transfer via CvP.

1’b0

RW