Reset signals, Reset signals –24 – Altera Arria V Hard IP for PCI Express User Manual

Page 122

7–24

Chapter 7: IP Core Interfaces

Arria V Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

Reset Signals

describes the reset signals.

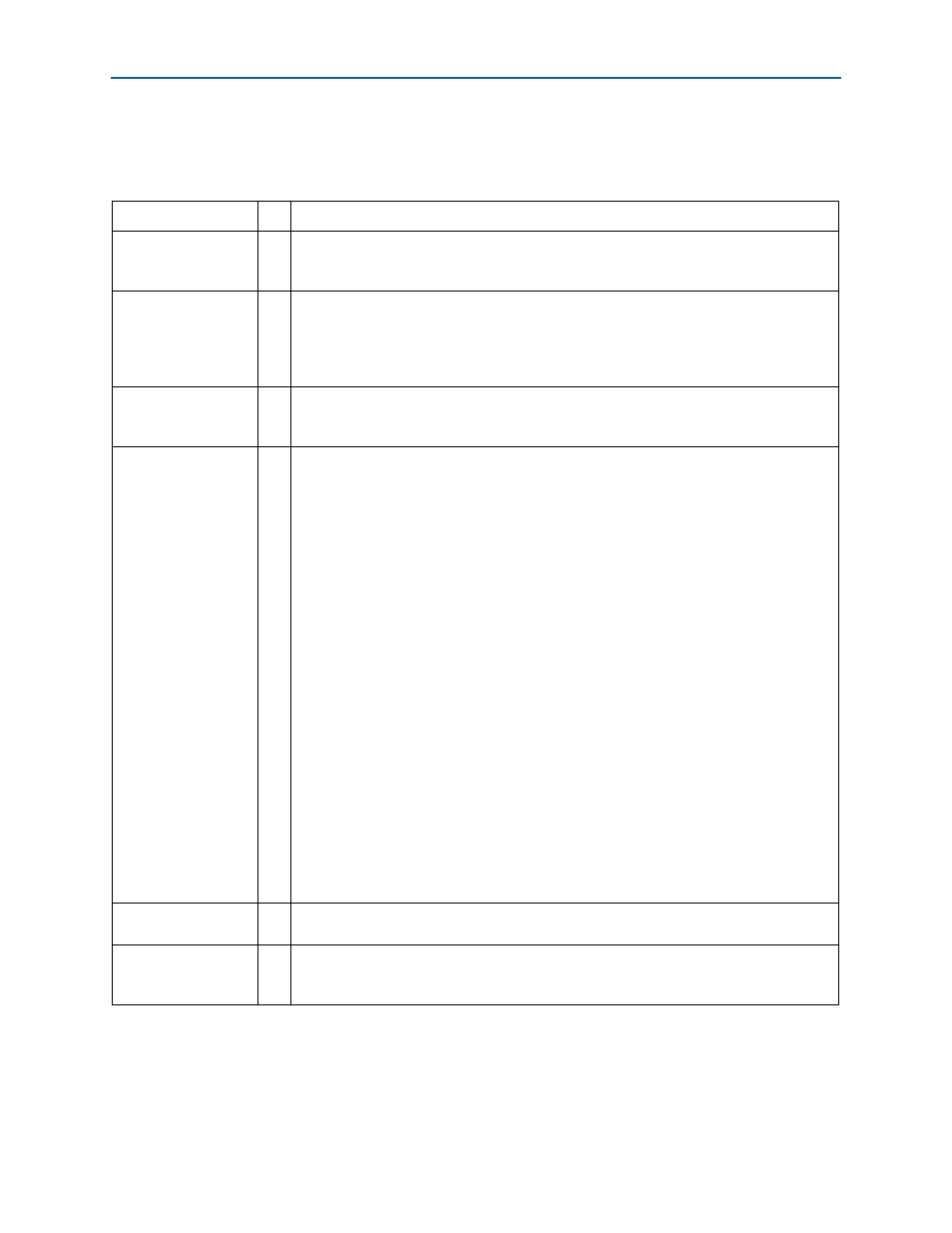

Table 7–6. Reset and Link Training Signals (Part 1 of 3)

Signal

I/O

Description

npor

I

Active low reset signal. It is the

OR

of

pin_perstn

and the

local_rstn

signal coming from

software Application Layer. If you do not drive a soft reset signal from the Application Layer,

this signal must be derived from

pin_perstn.

You cannot disable this signal.

reset_status

O

Active high reset status signal. When asserted, this signal indicates that the Hard IP clock is

in reset. The

reset_status

signal is synchronous to the

pld_clk

clock and is deasserted

only when the

npor

is deasserted and the Hard IP for PCI Express is not in reset

(

reset_status_hip

= 0). You should use

reset_status

to drive the reset of your

application.

nreset_status

O

For the Hard IP for PCI Express IP Core using the Avalon-MM interface,

nreset_status

is

an active low reset signal.

apps_rstn

, which is derived from

npor

or

pin_perstn

drives

nreset_status.

pin_perstn

I

Active low reset from the PCIe reset pin of the device. This reset signal is an input to the

embedded reset controller for PCI Express in Arria V devices. It resets the datapath and

control registers. This signal is required for CvP.

Although CvP is not supported in the current release, Altera is providing the following

information about the placement of the

pin_perstn

pins to facilitate advanced layout of

PCBs. Arria V devices have 1 or 2 instances of the Hard IP for PCI Express. Each instance

has its own

pin_perstn

signal.

Arria V devices have a

nPERST

pin for each available instance of the Hard IP for PCI Express.

These pins have the following locations:

■

nPERSTL0

: bottom left Hard IP and CvP blocks

■

nPERSTL1

: top left Hard IP block

For maximum use of the Arria V device, Altera recommends that you use the bottom left

Hard IP first. This is the only location that supports CvP over a PCIe link.

Refer to the appropriate Arria V device pinout for correct pin assignment for more detailed

informa

specifies this pin to require 3.3 V. You can drive this 3.3V signal to the

pin_perst

pin even

if the V

CCIO

of the bank is not 3.3V if the following 2 conditions are met:

■

The input signal meets the V

IH

and V

IL

specification for LVTTL.

■

The input signal meets the overshoot specification for 100

°

C operation as specified by the

“Maximum Allowed Overshoot and Undershoot Voltage” section

1 of the Arria Device Handbook.

for a timing diagram illustrating the use of this signal.

serdes_pll_locked

O

When asserted, indicates that the PLL that generates the

coreclkout_hip

clock signal is

locked. In pipe simulation mode this signal is always asserted.

pld_core_ready

I

When asserted, indicates that the Application Layer is ready for operation and is providing a

stable clock to the

pld_clk

input. If the

coreclkout_hip

Hard IP output clock is sourcing

the

pld_clk

Hard IP input, this input can be connected to the

serdes_pll_locked

output.