Pclk, Pclk –5, Illus – Altera Arria V Hard IP for PCI Express User Manual

Page 185

Chapter 9: Reset and Clocks

9–5

Clocks

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

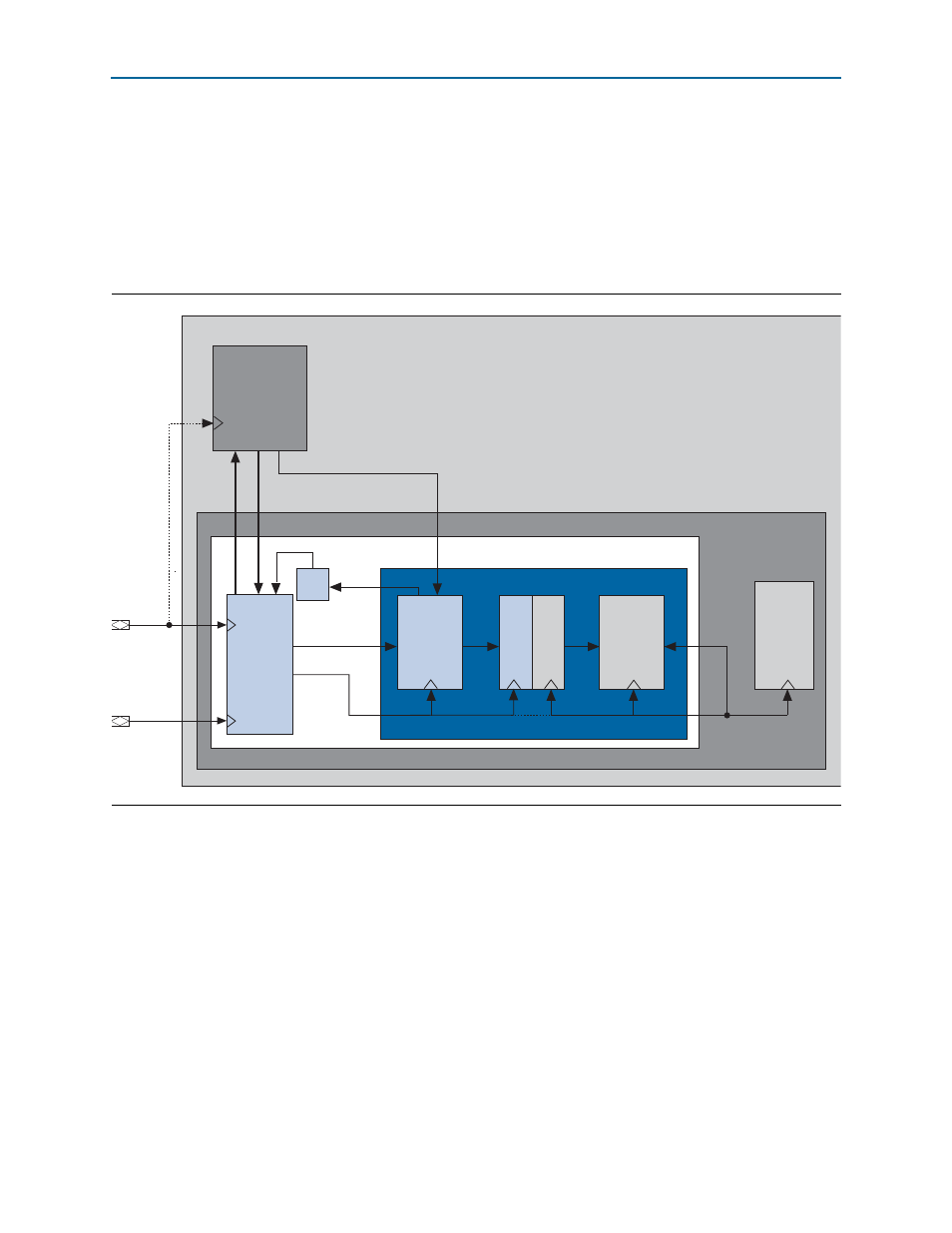

The Hard IP contains a clock domain crossing (CDC) synchronizer at the interface

between the PHY/MAC and the DLL layers which allows the Data Link and

Transaction Layers to run at frequencies independent of the PHY/MAC and provides

more flexibility for the user clock interface. Depending on system requirements, you

can use this additional flexibility to enhance performance by running at a higher

frequency for latency optimization or at a lower frequency to save power.

illustrates the clock domains.

indicates, there are three clock domains:

■

■

■

pclk

The transceiver derives

pclk

from the 100 MHz

refclk

signal that you must provide

to the

equires that the

refclk

signal

frequency be 100 MHz

±

300 PPM; however, as a convenience, you can also use a

reference clock that is 125 MHz

±

300 PPM.

Figure 9–5. Arria V Hard IP for PCI Express Clock Domains

100 MHz

(or 125 MHz)

100 MHz

(or 125 MHz)

Required for CvP

Hard IP for PCI Express

PHY/MAC

Clock

Domain

Crossing

(CDC)

Data Link

and

Transaction

Layers

125 or 250 MHz

pclk

refclk

reconfig_clk

data

PHY IP

Core for

PCIe

top_serdes.v

altpcie_a5_hwtcl.v

top.v

top_hw.v

(coreclkout is derived from p_clk)

reconfig_fromxcvr[

<n>

-1:0] reconfig_toxcvr[

<n>

-1:0]

reconfig_busy

rs_serdes

mgmt_clk_clk

coreclkout_hip

(62.5 or 125 MHz)

coreclkout

Application

Layer

Transceiver

Reconfiguration

Controller

pld_clk

(TX/RX

PCS/PMA)

Reset