Altera Arria V Hard IP for PCI Express User Manual

Page 139

Chapter 7: IP Core Interfaces

7–41

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Table 7–18

shows the layout of the Power Management Capabilities register.

describes the use of the various fields of the Power Management

Capabilities register.

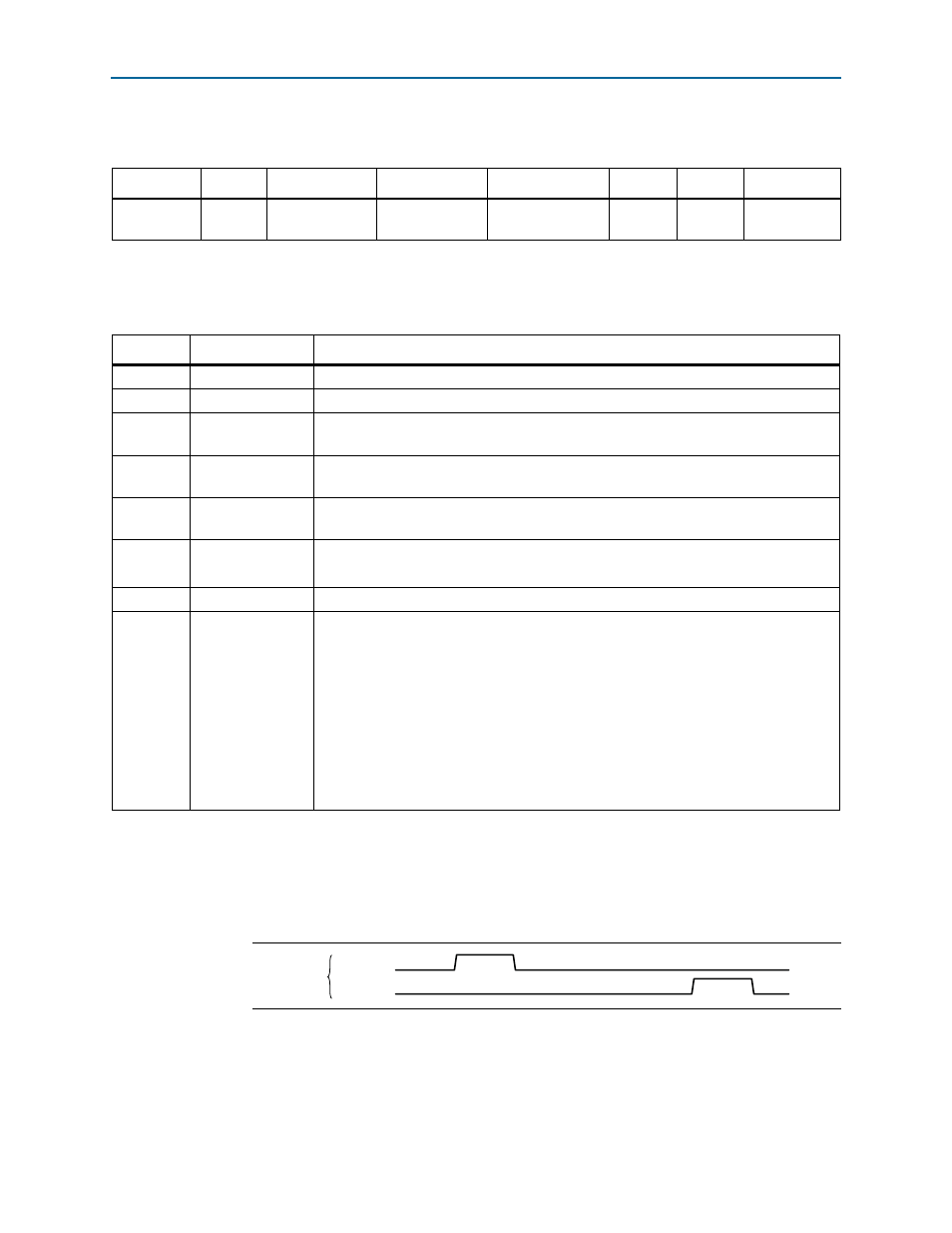

illustrates the behavior of

pme_to_sr

and

pme_to_cr

in an Endpoint. First,

the Hard IP receives the

PME_turn_off

message which causes

pme_to_sr

to assert.

Then, the Application Layer sends the

PME_to_ack

message to the Root Port by

asserting

pme_to_cr

.

Table 7–18. Power Management Capabilities Register

31

24

22

16

15

14

13 12

9

8

7

2

1

0

data

register

rsvd

PME_status

data_scale

data_select

PME_EN

rsvd

PM_state

Table 7–19. Power Management Capabilities Register Field Descriptions

Bits

Field

Description

[31:24]

Data register

This field indicates in which power states a function can assert the

PME# message

.

[22:16]

reserved

—

[15]

PME_status

When set to 1, indicates that the function would normally assert the

PME#

message

independently of the state of the

PME_en

bit.

[14:13]

data_scale

This field indicates the scaling factor when interpreting the value retrieved from the data

register. This field is read-only.

[12:9]

data_select

This field indicates which data should be reported through the data register and the

data_scale

field.

[8]6

PME_EN

1: indicates that the function can assert PME#

0: indicates that the function cannot assert PME#

[7:2]

reserved

—

[1:0]

PM_state

Specifies the power management state of the operating condition being described. The

following encodings are defined:

■

2b’00 D0

■

2b’01 D1

■

2b’10 D2

■

2b’11 D3

A device returns 2b’11 in this field and

Aux

or

PME Aux

in the

type

register to specify

the D3-Cold PM state. An encoding of 2b’11 along with any other

type

register value

specifies the D3-Hot state.

Figure 7–33. pme_to_sr and pme_to_cr in an Endpoint IP core

pme_to_sr

pme_to_cr

hard

IP