Debug features, Debug features –5 – Altera Arria V Hard IP for PCI Express User Manual

Page 13

Chapter 1: Datasheet

1–5

Debug Features

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

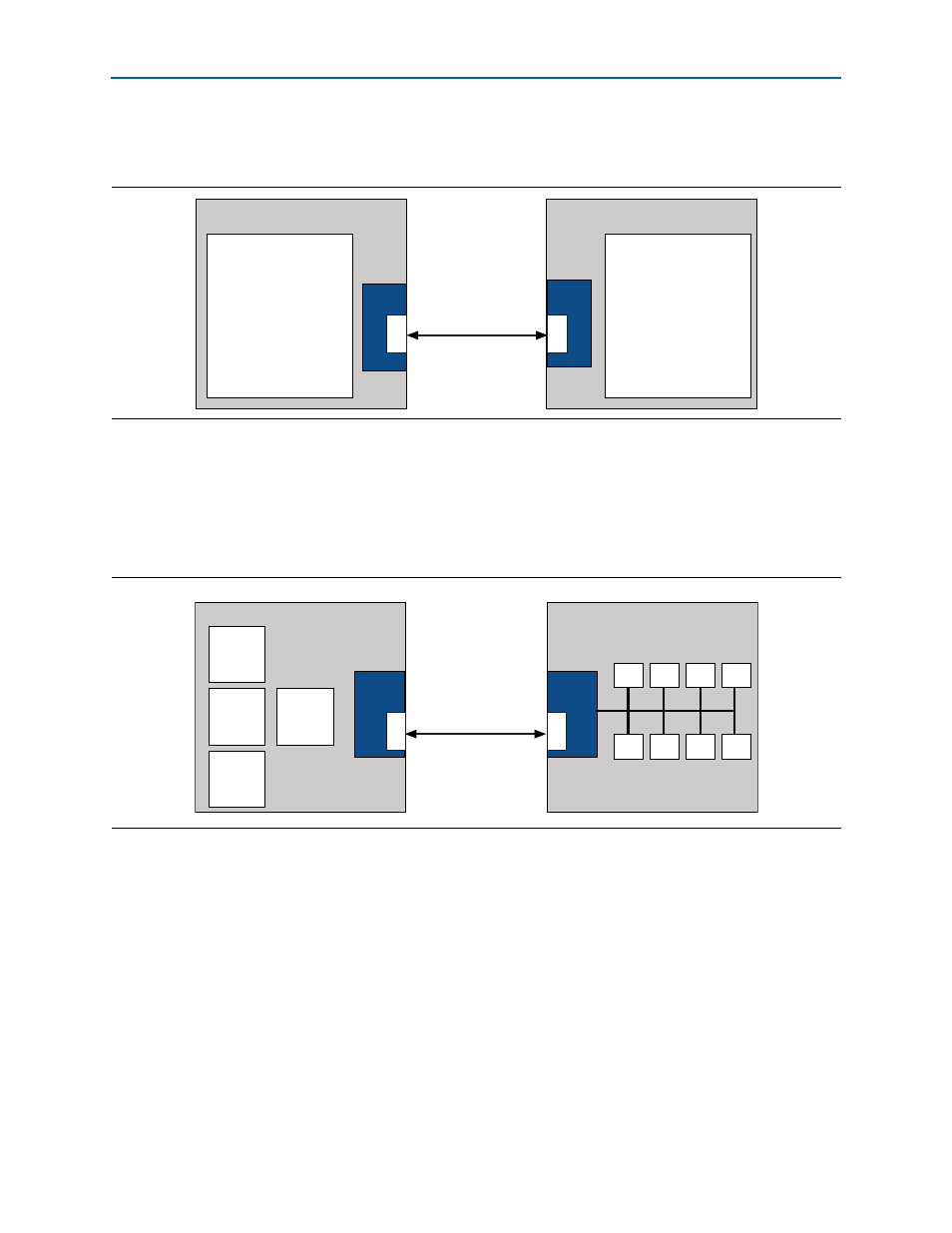

shows a PCI Express link between two Arria V FPGAs. One is configured

as a Root Port and the other as an Endpoint.

shows a PCI Express link between two Altera FPGAs. One is configured as

a Root Port and the other as a multi-function Endpoint. The FPGA serves as a custom

I/O hub for the host CPU. In the Arria V FPGA, each peripheral is treated as a

function with its own set of Configuration Space registers. Eight multiplexed

functions operate using a single PCI Express link.

Debug Features

The Arria V Hard IP for PCI Express includes debug features that allow observation

and control of the Hard IP for faster debugging of system-level problems. For more

information about debugging refer to

Chapter 19, C**Debugging

.

Figure 1–1. PCI Express Application with a Single Root Port and Endpoint

Altera FPGA

User Application

Logic

PCIe

Hard IP

RP

PCIe

Hard IP

EP

User Application

Logic

PCI Express Link

Altera FPGA

Figure 1–2. PCI Express Application with an Endpoint Using the Multi-Function Capability

Arria V or Cyclone V FPGA

PCIe Hard

IP Multi-

Function

EP

CAN

GbE

ATA

PCI

Altera FPGA

PCIe

Hard IP

RP

Host

CPU

Memory

Controller

Peripheral

Controller

Peripheral

Controller

USB

SPI

GPIO

I2C

PCI Express Link