Reset and clocks, Reset, Chapter 9. reset and clocks – Altera Arria V Hard IP for PCI Express User Manual

Page 181: Reset –1, Chapter 9, reset and clocks

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

9. Reset and Clocks

This chapter covers the functional aspects of the reset and clock circuitry for the Arria

V Hard IP for PCI Express. It includes the following sections:

■

■

For descriptions of the available reset and clock signals refer to

.

Reset

Hard IP for PCI Express includes two types of embedded reset controllers. One reset

controller is implemented in soft logic. A second reset controller is implemented in

hard logic. Software selects the appropriate reset controller depending on the

configuration you specify. Both reset controllers reset the Hard IP for PCI Express IP

Core and provide sample reset logic in the example design.

Figure 9–1 on page 9–2

provides a simplified view of the logic that implements both reset controllers.

Table 9–1

summarizes their functionality.

1

Contact Altera if you are designing with a Gen1 variant and want to use the soft reset

controller.

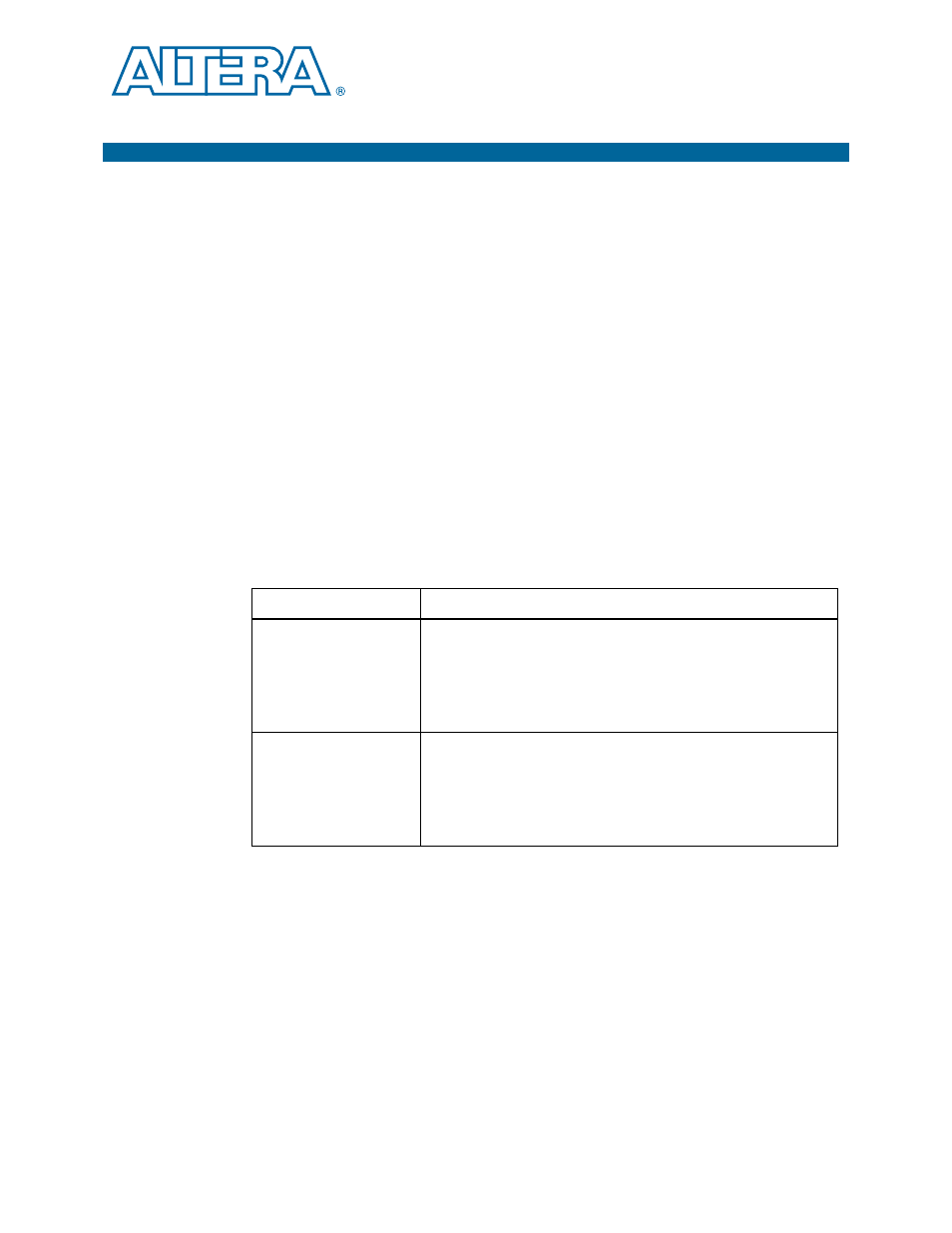

Table 9–1. Use of Hard and Soft Reset Controllers

Reset Controller Used

Description

Hard Reset Controller

pin_perstn

from the input pin of the FPGA resets the Hard IP for PCI

Express IP Core.

npor

is asserted if either

pin_perstn

or

local_rstn

is asserted. Application Layer logic generates the

optional

local_rstn

signal.

app_rstn

which resets the Application

Layer logic is derived from

npor

. This reset controller is used for

Gen1 ES devices and Gen 1 and Gen2 production devices.

Soft Reset Controller

Either

pin_perstn

from the input pin of the FPGA or

npor

which is

derived from

pin_perstn

or

local_rstn

can reset the Hard IP for

PCI Express IP Core. Application Layer logic generates the optional

local_rstn

signal.

app_rstn

which resets the Application Layer

logic is derived from

npor

. This reset controller is used for Gen2 ES

devices and Gen3 ES and production devices.

December 2013

UG-01110-1.5