Port functions, Parameters shared across all port functions, Port functions –3 – Altera Arria V Hard IP for PCI Express User Manual

Page 55: Parameters shared across all port functions –3

Chapter 4: Parameter Settings for the Arria V Hard IP for PCI Express

4–3

Port Functions

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Port Functions

This section describes the parameter settings for port functions. It includes the

following sections:

■

Parameters Shared Across All Port Functions

■

Parameters Defined Separately for All Port Functions

Parameters Shared Across All Port Functions

This section defines the PCI Express and PCI capabilities parameters that are shared

for all port functions. It includes the following capabilities:

■

■

■

■

■

1

Text in

green

are links to these parameters stored in the

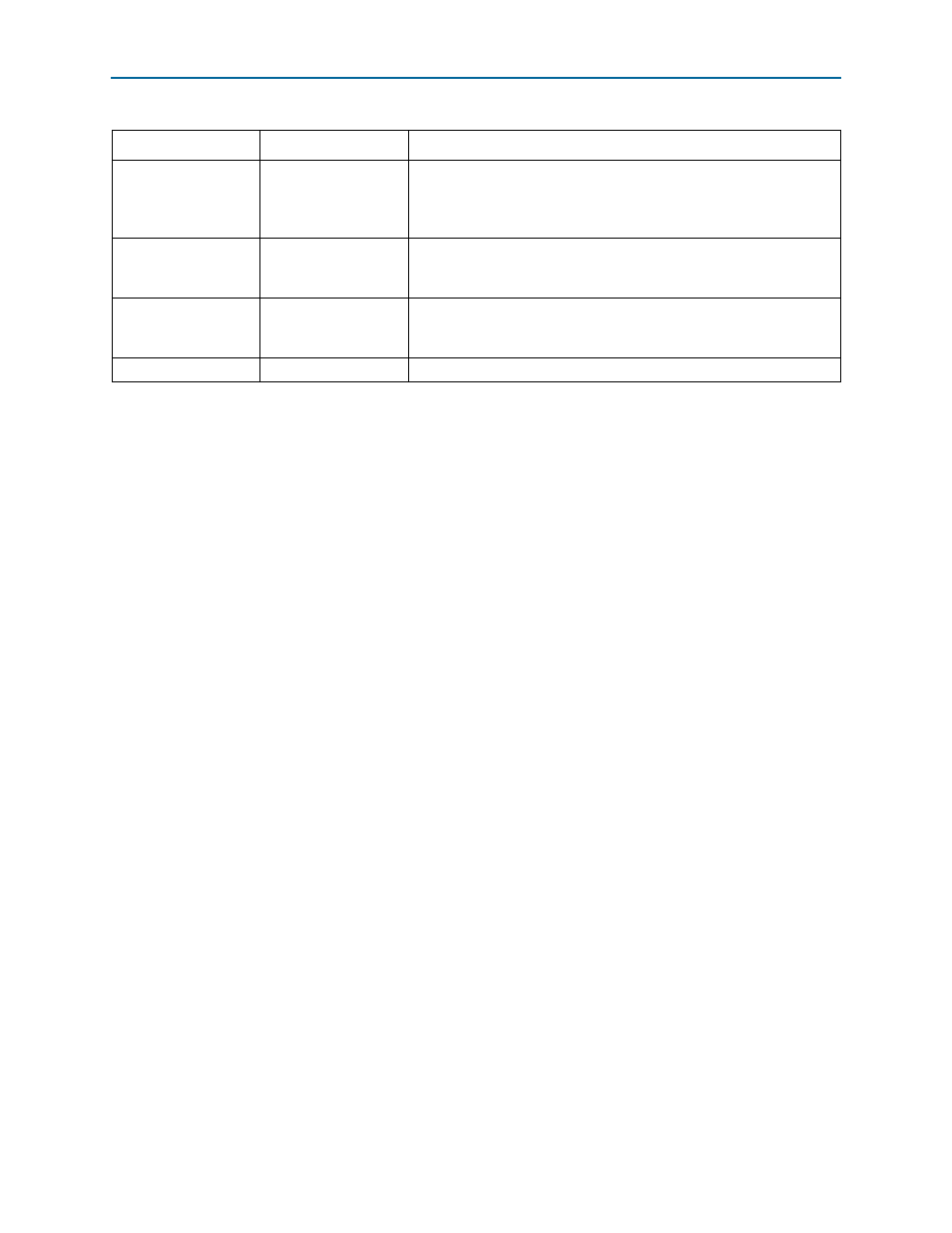

Reference clock

frequency

100 MHz

125 MHz

The

quires a

100 MHz

±

300 ppm reference clock. The 125 MHz reference clock is

provided as a convenience for systems that include a 125 MHz clock

source.

Use 62.5 MHz

Application Layer

clock

On/Off

This mode is only available for Gen1 ×1 variants.

Use deprecated RX

Avalon-ST data byte

enable port (rx_st_be)

On/Off

When enabled the variant includes the deprecated

rx_st_be

signals.

The byte enable signals may not be available in future releases. Altera

recommends that you leave this option Off for new designs.

Number of functions

1–8

Specifies the number of functions that share the same link.

Table 4–1. System Settings for PCI Express (Part 3 of 3)

Parameter

Value

Description